FPGA データの取得

RFSoC デバイスから MATLAB または Simulink にデータを取得する

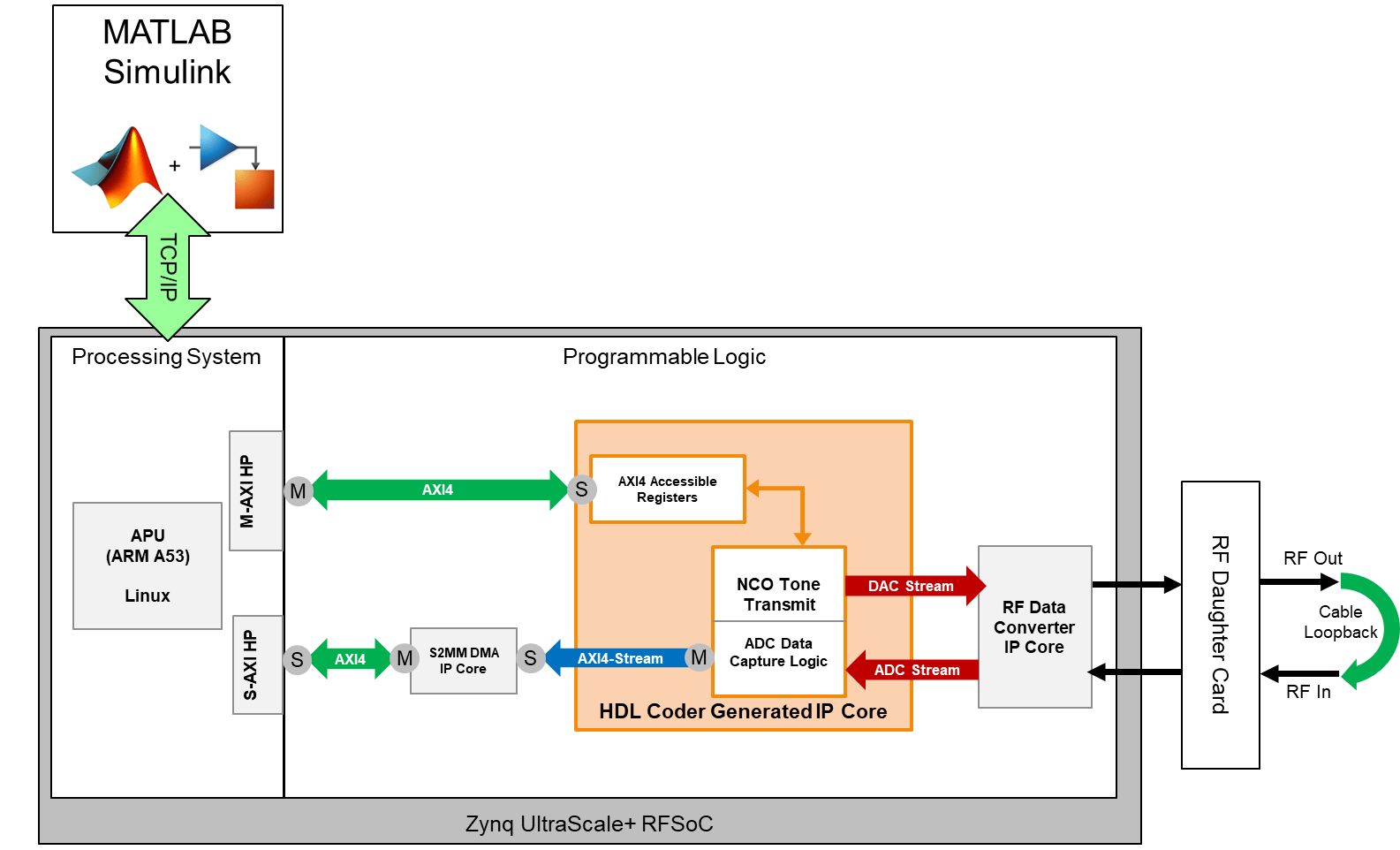

RFSoC デバイスから FPGA 入出力 (IO) アプリケーション プログラミング インターフェイス (API) を使用して生データを取得します。HDL ワークフロー アドバイザーを使用して、HDL コードの生成用に SoC モデルを構成します。アルゴリズムの HDL コードを生成し、HDL 設計をビルドして RFSoC デバイスに展開し、MATLAB® スクリプトを実行して展開済みの HDL 設計から対話的にデータを取得します。

トピック

- ARM Targeting

Design and deploy algorithms to the ARM® processor.

- Reference Designs for RFSoC Devices

Learn about how to use RFSoC reference designs and their requirements.