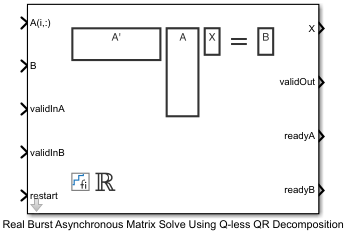

Real Burst Asynchronous Matrix Solve Using Q-less QR Decomposition

ライブラリ:

Fixed-Point Designer HDL Support /

Matrices and Linear Algebra /

Linear System Solvers

説明

Real Burst Asynchronous Matrix Solve Using Q-less QR Decomposition ブロックは非同期の Q-less QR 分解を使用して連立線形方程式 A'AX = B を解きます。ここで A と B は実数値の行列です。

正則化パラメーターが非ゼロの場合、Real Burst Asynchronous Matrix Solve Using Q-less QR Decomposition ブロックは次の行列方程式を解きます。

ここで、λ は正則化パラメーター、A は m 行 n 列の行列、In = eye(n) です。

このブロックは非同期的に動作します。前進代入および後退代入と Q-less QR 分解は、最新の R 行列と B 行列を使用して個別に実行されます。

例

ハードウェア効率に優れた Real Burst Asynchronous Matrix Solve Using Q-less QR Decomposition の実装

この例では、Real Burst Asynchronous Matrix Solve Using Q-less QR Decomposition ブロックを使用して、実数値の行列方程式 A'AX=B に対するハードウェア効率に優れた解を実装する方法を示します。

端子

入力

実数行列 A の行。ベクトルとして指定します。A は m 行 n 列の行列で、m ≥ 2 および m ≥ n です。B が single または double の場合、A は B と同じデータ型でなければなりません。A が固定小数点データ型の場合、A は符号付きで、2 進小数点スケーリングを使用し、B と同じ語長をもたなければなりません。傾きとバイアス表現は固定小数点データ型ではサポートされていません。

データ型: single | double | fixed point

実数行列 B の行。ベクトルとして指定します。B は n 行 p 列の行列で、n ≥ 2 です。A が single または double の場合、B は A と同じデータ型でなければなりません。B が固定小数点データ型の場合、B は符号付きで、2 進小数点スケーリングを使用し、A と同じ語長をもたなければなりません。傾きとバイアス表現は固定小数点データ型ではサポートされていません。

データ型: single | double | fixed point

A(i,:) の入力が有効であるかどうか。boolean スカラーとして指定します。この制御信号は A(i,:) 入力端子からのデータが有効であるかどうかを示します。この値が 1 (true) で readyA の値が 1 (true) の場合、ブロックは A(i,:) 入力端子の値を取得します。この値が 0 (false) の場合、ブロックは入力サンプルを無視します。

true の validInA 信号を送信してから、readyA が false に設定されるまでに、多少の遅延が生じることがあります。すべてのデータが確実に処理されるように、別の true の validInA 信号を送信するときは、readyA が false に設定されるまで待たなければなりません。

データ型: Boolean

B の入力が有効であるかどうか。boolean スカラーとして指定します。この制御信号は B 入力端子からのデータが有効であるかどうかを示します。この値が 1 (true) で readyB の値が 1 (true) の場合、ブロックは B 入力端子の値を取得します。この値が 0 (false) の場合、ブロックは入力サンプルを無視します。

true の validInB 信号を送信してから、readyB が false に設定されるまでに、多少の遅延が生じることがあります。すべてのデータが確実に処理されるように、別の true の validInB 信号を送信するときは、readyB が false に設定されるまで待たなければなりません。

データ型: Boolean

内部状態をクリアするかどうか。boolean スカラーとして指定します。この値が 1 (true) の場合、ブロックは現在の計算を停止し、すべての内部状態をオフにします。この値が 0 (false) で validIn の値が 1 (true) の場合、ブロックは新しいサブフレームを開始します。

データ型: Boolean

出力

行列 X。行列またはベクトルとして返されます。

データ型: single | double | fixed point

出力データが有効であるかどうか。boolean スカラーとして指定します。この制御信号は出力端子 X のデータが有効であるかどうかを示します。この値が 1 (true) の場合、ブロックは行列 X を正常に計算しています。この値が 0 (false) の場合、出力データは有効ではありません。

データ型: Boolean

入力 A(i,:) に対するブロックの準備が整っているかどうか。boolean スカラーとして返されます。この制御信号は新しい入力データに対するブロックの準備が整っているかどうかを示します。この値が 1 (true) で validInA が 1 (true) の場合、ブロックは入力データを次のタイム ステップで受け入れます。この値が 0 (false) の場合、ブロックは入力データを次のタイム ステップで無視します。

true の validInA 信号を送信してから、readyA が false に設定されるまでに、多少の遅延が生じることがあります。すべてのデータが確実に処理されるように、別の true の validInA 信号を送信するときは、readyA が false に設定されるまで待たなければなりません。

データ型: Boolean

入力 B に対するブロックの準備が整っているかどうか。boolean スカラーとして返されます。この制御信号は新しい入力データに対するブロックの準備が整っているかどうかを示します。この値が 1 (true) で validInB が 1 (true) の場合、ブロックは入力データを次のタイム ステップで受け入れます。この値が 0 (false) の場合、ブロックは入力データを次のタイム ステップで無視します。

true の validInB 信号を送信してから、readyB が false に設定されるまでに、多少の遅延が生じることがあります。すべてのデータが確実に処理されるように、別の true の validInB 信号を送信するときは、readyB が false に設定されるまで待たなければなりません。

データ型: Boolean

パラメーター

行列 A の行数。正の整数値のスカラーとして指定します。

プログラムでの使用

ブロック パラメーター: m |

| 型: 文字ベクトル |

| 値: 正の整数値のスカラー |

既定の設定: 4 |

行列 A の列数と行列 B の行数。正の整数値のスカラーとして指定します。

プログラムでの使用

ブロック パラメーター: n |

| 型: 文字ベクトル |

| 値: 正の整数値のスカラー |

既定の設定: 4 |

行列 B の列数。正の整数値のスカラーとして指定します。

プログラムでの使用

ブロック パラメーター: p |

| 型: 文字ベクトル |

| 値: 正の整数値のスカラー |

既定の設定: 1 |

正則化パラメーター。非負のスカラーとして指定します。正則化パラメーターを小さい正の値にすると、問題の調整を向上させ、推定値の分散を小さくすることができます。バイアスがありますが、推定値の分散が小さいと、多くの場合、最小二乗推定値と比べて平均二乗誤差が小さくなります。

プログラムでの使用

ブロック パラメーター: regularizationParameter |

| 型: 文字ベクトル |

| 値: 非負の実数スカラー |

既定の設定: 0 |

出力行列 X のデータ型。fixdt(1,18,14)、double、single、fixdt(1,16,0)、またはユーザー指定のデータ型式として指定します。型は直接指定されるか、Simulink.NumericType などのデータ型オブジェクトとして表現されます。

プログラムでの使用

ブロック パラメーター: OutputType |

| 型: 文字ベクトル |

値: 'fixdt(1,18,14)' | 'double' | 'single' | 'fixdt(1,16,0)' | '<data type expression>' |

既定の設定: 'fixdt(1,18,14)' |

アルゴリズム

シストリック実装はスペースの制約よりも計算速度を優先します。一方、バーストによる実装は演算速度を犠牲にしてスペースの制約を優先します。次の表は、行列の分解と連立線形方程式の求解に使用できる実装間のトレードオフを示しています。

| 実装 | スループット | レイテンシ | 領域 |

|---|---|---|---|

| シストリック | 高 | O(nlog2(m)) | O(mn2) |

| 部分的なシストリック | 中 | O(mn) | O(n2) |

| バースト | 低 | O(mn) | O(n) |

m は行列 A の行数で、n は行列 A の列数です。アーキテクチャに関係なく、語長が大きくなるほど、スループットは低下し、レイテンシと回路面積は増大します。

用途に適したブロックの選択に関する追加の考慮事項については、Choose a Block for HDL-Optimized Fixed-Point Matrix Operationsを参照してください。

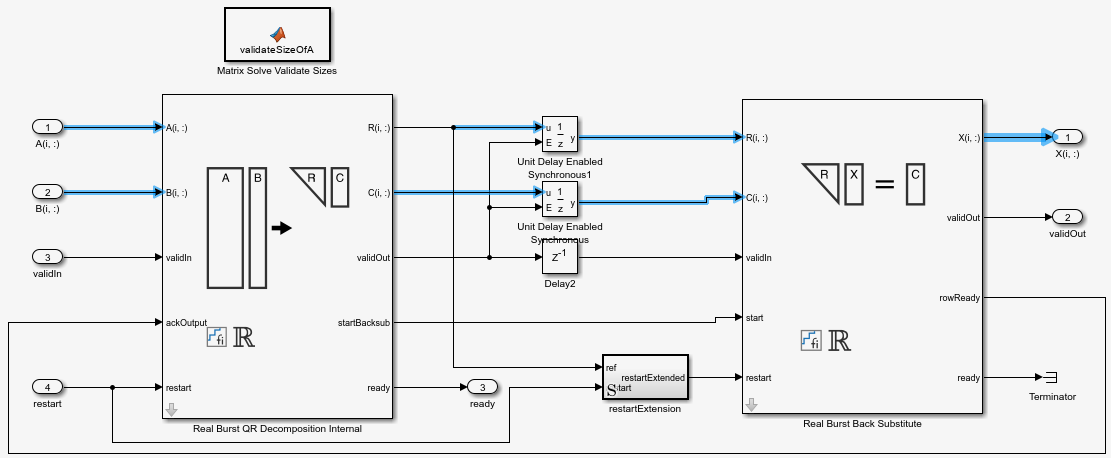

"Matrix Solve Using QR Decomposition" のブロックは同期的に動作します。これらのブロックでは、まず、入力行列 A と B が QR Decomposition ブロックを使用して行列 R と C に分解されます。次に、Back Substitute ブロックで RX = C が計算されます。入力行列 A と B が同期された方法で並行してシステムに伝播されます。

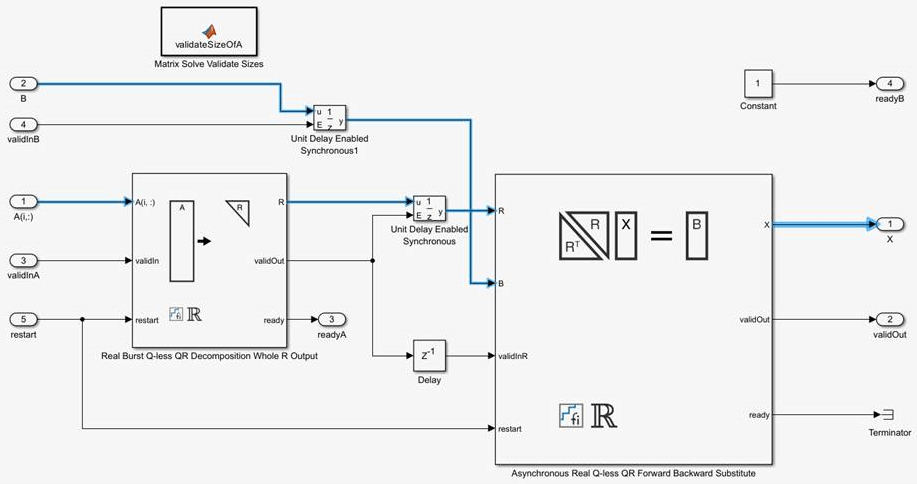

"Matrix Solve Using Q-less QR Decomposition" のブロックは非同期的に動作します。まず、入力行列 A の Q-less QR 分解が実行され、結果の行列 R がバッファーに格納されます。次に、Forward Backward Substitution ブロックで、入力行列 B とバッファーに格納された行列 R を使用して R'RX = B が計算されます。行列 R と行列 B がバッファーに別々に格納されるため、上流の Q-less QR Decomposition ブロックと下流の Forward Backward Substitute ブロックを独立して実行できます。Forward Backward Substitute ブロックによる処理は、1 つ目の行列 R と B が使用できるようになると開始されます。その後、Q-less QR Decomposition ブロックのステータスに関係なく、バッファーに格納された最新の行列 R と B を使用して連続的に実行されます。たとえば、上流のブロックからの行列 A と B の提供が停止すると、Forward Backward Substitute ブロックは行列 R と B の最後のペアを使用して同じ出力を生成し続けます。

"Burst (Asynchronous) Matrix Solve Using Q-less QR Decomposition" のブロックは、ブロック名に示されているように、同期演算と非同期演算の両方のバリアントで使用できます。

このブロックでは AMBA AXI ハンドシェイク プロトコル [1] を使用しています。データと制御情報の転送に valid/ready ハンドシェイク プロセスが使用されます。この双方向の制御メカニズムにより、マネージャーと配下の間で情報をやり取りするレートをマネージャーと配下の双方で制御できます。valid 信号はデータが使用可能であることを示します。ready 信号はブロックでデータを受け入れ可能であることを示します。valid 信号と ready 信号の両方が High の場合にのみデータの転送が行われます。

"Burst Asynchronous Matrix Solve Using Q-less QR Decomposition" のブロックは、行列 A を行単位で受け入れ、行列 B を単一のベクトルとして受け入れます。行列 A と B の最初の有効なペアを受け入れた後、ブロックは行列 X を行単位で連続的に出力します。行列は最初の行から最後の行まで出力されます。

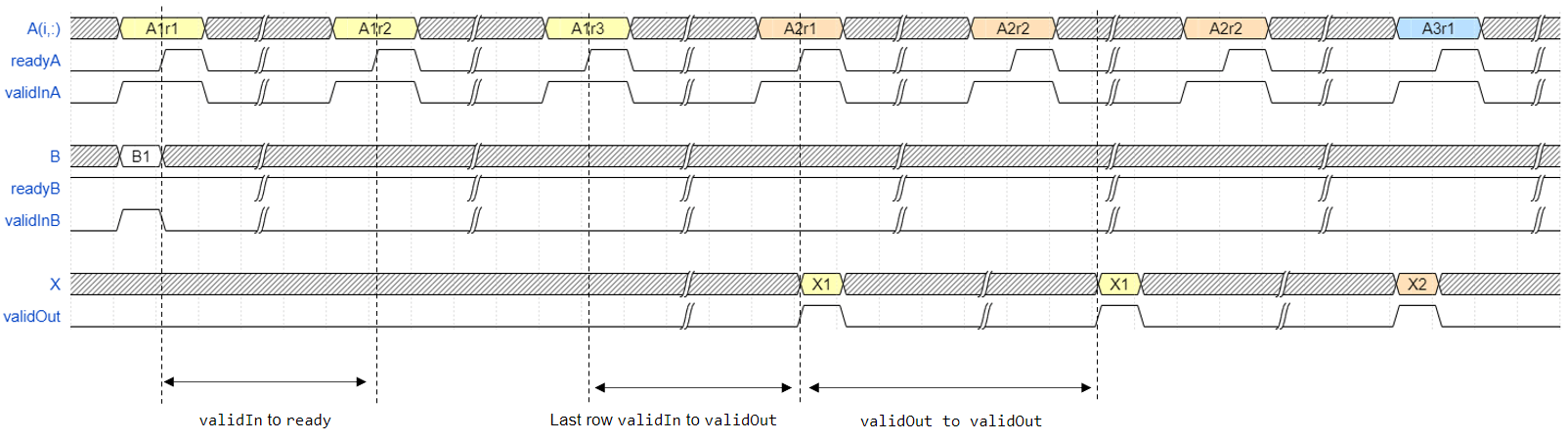

たとえば、入力行列 A が 3 行 3 列であるとします。また、validIn のアサートが ready よりも前、つまり上流のデータ ソースが QR 分解よりも速いと仮定します。

この図で次のとおりです。

A1r1は 1 つ目の行列 A の 1 行目、A1r2は 1 つ目の行列 A の 2 行目などのようになります。validInからreadyまで — A の行が正常に入力されてから、ブロックで次の行の受け入れ準備ができるまで。validOutからvalidOutまで — Forward Backward Substitution ブロックは連続的に実行されるため、一定のレートで出力が生成されます。これは隣接する 2 つの有効な出力間の遅延です。最後の行の

validInからvalidOutまで — 最後の m 番目の行が入力されてから、ブロックで解の出力が開始されるまで。このブロックは常に行列 B を受け入れる準備ができているため、

readyBは常にアサートされます。

次の表に、Real Burst Asynchronous Matrix Solve Using Q-less QR Decomposition ブロックのタイミングの詳細を示します。レイテンシは、行列 A のサイズと、行列 A および B のデータ型によって異なります。表内では以下のようになっています。

n は行列 A の列数です。

wl は行列 A の入力データの語長を表します。

| 入力データ型 | validIn から ready まで (サイクル) | validOut から validOut まで (サイクル) | 最後の行の validIn から validOut まで (サイクル) |

|---|---|---|---|

固定小数点 fi | (wl + 5)*n + 2 + (n + 1) | 4*n2 + 25*n + 5 + 2*n*wl + 2*n*nextpow2(wl) | 4*n2 + 25*n + 5 + 2*n*wl + 2*n*nextpow2(wl) + (wl + 5)*n + n |

スケーリングされた double の fi | (wl + 5)*n + 2 + (n + 1) | 4*n2 + 23*n + 5 + 2*n*wl | 4*n2 + 24*n + 5 + 2*n*wl + (wl + 5)*n |

double | 59*n + 3 | 4*n2 + 21*n + 5 | 4*n2 + 80*n + 5 |

single | 30*n + 3 | 4*n2 + 21*n + 5 | 4*n2 + 51*n + 5 |

このブロックは、Simulink® HDL ワークフロー アドバイザーを使用した HDL コード生成をサポートしています。例については、Simulink モデルからの HDL コード生成と FPGA 合成 (HDL Coder)およびImplement Digital Downconverter for FPGA (DSP HDL Toolbox)を参照してください。

この例のデータは、Xilinx® Zynq® UltraScale™ + RFSoC ZCU111 評価ボードでブロックを合成して生成したものです。合成ツールは Vivado® v.2020.2 (win64) です。

合成に使用したパラメーターは次のとおりです。

ブロック パラメーター:

m = 16n = 16p = 1行列 A の次元: 16 行 16 列

行列 B の次元: 16 行 1 列

入力データ型:

sfix16_En14ターゲット周波数: 250 MHz

次の各表に、配置配線後のリソース使用状況の結果とタイミングの概要をそれぞれ示します。

| リソース | 使用 | 使用可能 | 使用率 (%) |

|---|---|---|---|

| CLB LUT | 16131 | 425280 | 3.79 |

| CLB レジスタ | 21469 | 850560 | 2.52 |

| DSP | 4 | 4272 | 0.09 |

| ブロック RAM タイル | 0 | 1080 | 0.00 |

| URAM | 0 | 80 | 0.00 |

| 値 | |

|---|---|

| 要件 | 4 ns |

| データ パス遅延 | 3.544 ns |

| スラック | 0.437 ns |

| クロック周波数 | 280.66 MHz |

参照

[1] "AMBA AXI and ACE Protocol Specification Version E." https://developer.arm.com/documentation/ihi0022/e/

拡張機能

傾きとバイアス表現は固定小数点データ型ではサポートされていません。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加のコンフィギュレーション オプションがあります。

このブロックには 1 つの既定の HDL アーキテクチャがあります。

| 一般 | |

|---|---|

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

固定小数点データ型のみをサポートします。

固定小数点の変換

Fixed-Point Designer™ を使用して固定小数点システムの設計とシミュレーションを行います。

バージョン履歴

R2022b で導入

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)