Logo Recognition Network

This example shows how to create, compile, and deploy a dlhdl.Workflow object that has Logo Recognition Network as the network object using the Deep Learning HDL Toolbox™ Support Package for Xilinx FPGA and SoC. Use MATLAB® to retrieve the prediction results from the target device.

The Logo Recognition Network

Logos assist users in brand identification and recognition. Many companies incorporate their logos in advertising, documentation materials, and promotions. The logo recognition network (logonet) was developed in MATLAB® and can recognize 32 logos under various lighting conditions and camera motions. Because this network focuses only on recognition, you can use it in applications where localization is not required.

Prerequisites

Xilinx ZCU102 SoC development kit

Load the Pretrained Series Network

To load the pretrained series network logonet, enter:

snet = getLogoNetwork;

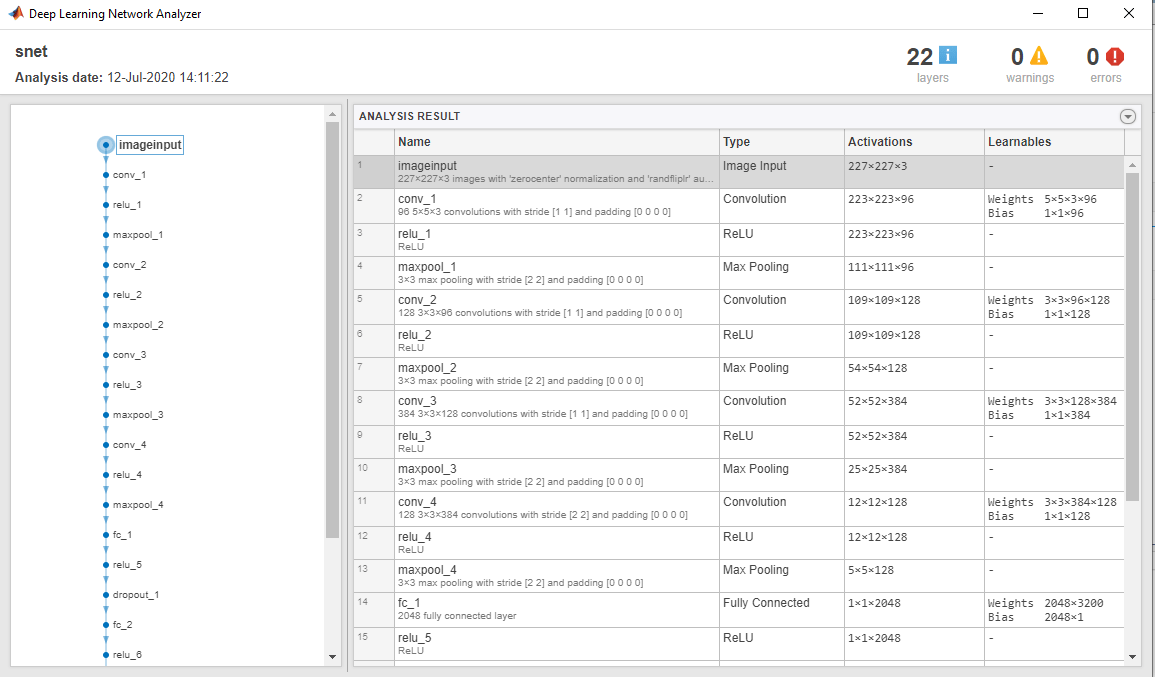

To view the layers of the pretrained series network, enter:

analyzeNetwork(snet)

Create Target Object

Create a target object that has a custom name for your target device and an interface to connect your target device to the host computer. Interface options are JTAG and Ethernet. To use JTAG, install Xilinx™ Vivado™ Design Suite 2022.1. To set the Xilinx Vivado toolpath, enter:

% hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath', 'C:\Xilinx\Vivado\2022.1\bin\vivado.bat');To create the target object, enter:

hTarget = dlhdl.Target('Xilinx','Interface','Ethernet');

Create WorkFlow Object

Create an object of the dlhdl.Workflow class. When you create the object, specify the network and the bitstream name. Specify the saved pretrained logonet neural network, snet, as the network. Make sure that the bitstream name matches the data type and the FPGA board that you are targeting. In this example the target FPGA board is the Xilinx ZCU102 SOC board. The bitstream uses a single data type.

hW = dlhdl.Workflow('network', snet, 'Bitstream', 'zcu102_single','Target',hTarget); % If running on Xilinx ZC706 board, instead of the above command, % uncomment the command below. % % hW = dlhdl.Workflow('Network', snet, 'Bitstream', 'zc706_single','Target',hTarget);

Compile the Logo Recognition Network

To compile the logo recognition network, run the compile function of the dlhdl.Workflow object.

dn = hW.compile

offset_name offset_address allocated_space

_______________________ ______________ _________________

"InputDataOffset" "0x00000000" "24.0 MB"

"OutputResultOffset" "0x01800000" "4.0 MB"

"SystemBufferOffset" "0x01c00000" "60.0 MB"

"InstructionDataOffset" "0x05800000" "12.0 MB"

"ConvWeightDataOffset" "0x06400000" "32.0 MB"

"FCWeightDataOffset" "0x08400000" "44.0 MB"

"EndOffset" "0x0b000000" "Total: 176.0 MB"

dn = struct with fields:

Operators: [1×1 struct]

LayerConfigs: [1×1 struct]

NetConfigs: [1×1 struct]

Program Bitstream onto FPGA and Download Network Weights

To deploy the network on the Xilinx ZCU102 SoC hardware, run the deploy function of the dlhdl.Workflow object. This function uses the output of the compile function to program the FPGA board by using the programming file. It also downloads the network weights and biases. The deploy function starts programming the FPGA device, displays progress messages, and the time it takes to deploy the network.

hW.deploy

### FPGA bitstream programming has been skipped as the same bitstream is already loaded on the target FPGA. ### Loading weights to FC Processor. ### 33% finished, current time is 28-Jun-2020 12:40:14. ### 67% finished, current time is 28-Jun-2020 12:40:14. ### FC Weights loaded. Current time is 28-Jun-2020 12:40:14

Load the Example Image

Load the example image.

image = imread('heineken.png');

inputImg = imresize(image, [227, 227]);

imshow(inputImg);

Run the Prediction

Execute the predict function on the dlhdl.Workflow object and display the result:

[prediction, speed] = hW.predict(single(inputImg),'Profile','on');

### Finished writing input activations. ### Running single input activations.

Deep Learning Processor Profiler Performance Results

LastLayerLatency(cycles) LastLayerLatency(seconds) FramesNum Total Latency Frames/s

------------- ------------- --------- --------- ---------

Network 38865102 0.17666 1 38865144 5.7

conv_module 34299592 0.15591

conv_1 6955899 0.03162

maxpool_1 3306384 0.01503

conv_2 10396300 0.04726

maxpool_2 1207215 0.00549

conv_3 9269094 0.04213

maxpool_3 1367650 0.00622

conv_4 1774679 0.00807

maxpool_4 22464 0.00010

fc_module 4565510 0.02075

fc_1 2748478 0.01249

fc_2 1758315 0.00799

fc_3 58715 0.00027

* The clock frequency of the DL processor is: 220MHz

[val, idx] = max(prediction);

snet.Layers(end).ClassNames{idx}ans = 'heineken'

See Also

dlhdl.Workflow | dlhdl.Target | compile | deploy | predict