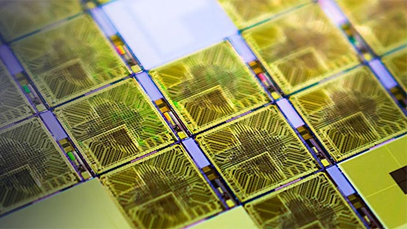

モデルベースデザインによるFPGA/ASIC実装【オンライン無料体験会】

概要

新しい設計手法を学んで、FPGA/ASIC設計効率を改善しませんか?

本体験会は、実際にモデルベースデザインによるFPGA /ASIC設計フローを体験することができるコースです。Simulinkモデル作成からHDLコード生成、HDL/FPGA検証までの基本的な操作方法を習得していただき、ご導入可否の判断にお役立ていただくことができる内容となっています。

当日は、MATLABの操作体験をしながら、適宜講演者にご質問いただけます。

モデルベースデザインによるFPGA/ASIC設計には次のような利点があります。

- システム・シミュレーションによる機能検証で品質向上

- ブロック線図により設計資産の再利用性向上と、コード生成レポートによりトレーサビリティ向上

- コード生成により、コード記述及びテストベンチ作成工数やデバッグ工数の削減、品質向上

ハイライト

- HDL生成のための設定と手順

- HDL生成に対応したSimulinkモデルの作成例

- 固定小数点化とシミュレーション

- 最適化(リソース共有、パイプライン)機能

- 等価性検証および検証の高速化

- 論理合成ツール(Intel Quartus/Xilinx Vivado)との連携

参加対象者

HDL Coder 未導入で今後導入を検討されている方

※オンライン(Cisco WebEx Event)で実施いたします。参加者には事前にMATLABを体験できる評価版を発行します。MATLABを利用可能なPCを各自ご用意下さい。講師の画面とご自身の画面を見られるよう2画面でのご利用を推奨いたします。聴講だけのご参加も可能です。

※定員等の都合により、参加をお断りする場合があります。あらかじめご了承ください。

※既に導入済みの方は、2月28~29日に実施される技術トレーニング「HDL Coder による HDL コード生成」コースのご受講下さい。

講演者について

マスワークス プリンシパル・HDLプロダクトスペシャリスト 松本 充史

電子機器メーカーにて信号処理アルゴリズム開発、電子回路設計に従事後、MATLABの国内代理店にアプリケーションエンジニアとして入社し、信号処理・画像処理、C、HDLコード生成などを担当。現在は主にFPGA/ASIC実装分野のアプリケーションエンジニアとして、ユーザのサポート、機能やユーザビリティ向上のための活動を中心に行っている。

アジェンダ

| 時間 | タイトル |

| 13:00 | 開場(オンラインオープン) |

| 13:30 | 体験会開始 |

| 17:30 | 体験会終了、Q&A |