Frame To Samples

Convert frame-based data to sample stream

Libraries:

Wireless HDL Toolbox /

I/O Interfaces

Description

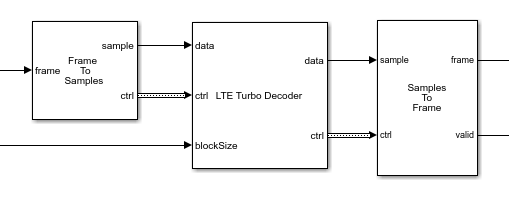

The Frame To Samples block flattens frame-based input into a stream of samples. The block also returns a stream of corresponding control signals that indicate sample validity and the boundaries of the frame. You can configure idle cycles inserted between samples or between frames, and how many values represent each sample. See Streaming Sample Interface for details of the streaming format.

Use this block to generate input for a subsystem targeted for HDL code generation. This block does not support HDL code generation.

Examples

Ports

Input

Output

Parameters

Extended Capabilities

Version History

Introduced in R2017b