SoC Generation Workflows

SoC Blockset™ offers several workflows for generating bitstreams, software, and deploying your model on an SoC device.

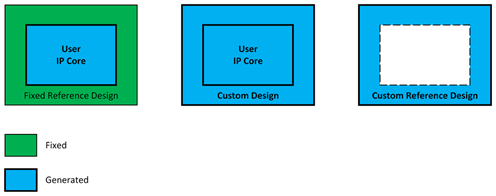

IP core generation workflow: Use a provided architecture (fixed reference design), and use Simulink® to design your IP core.

SoC builder workflow: Use Simulink to design an architecture and an IP core from scratch.

Export reference design: Use Simulink to export your architecture as a custom reference design, leaving a placeholder for IP generation downstream.

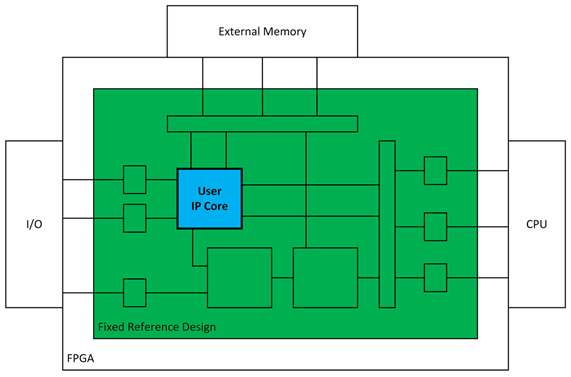

IP Core Generation Workflow

In this workflow, SoC Blockset provides the system architecture as a fixed reference design. You can then design your IP core with Simulink. The IP core generation workflow takes you through the steps to integrate your IP in the fixed reference design, generate HDL code and deploy on hardware. For an example using this workflow, see Use IP Core Generation Workflow with SoC Models.

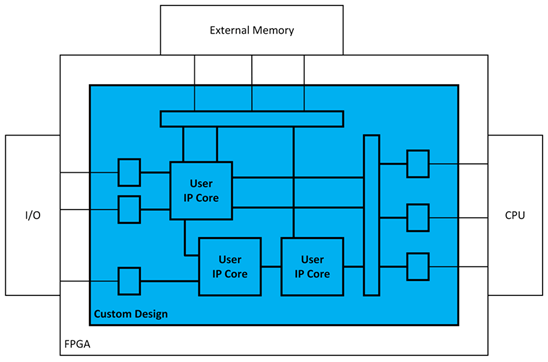

SoC Builder Workflow

In this workflow, you design the whole system, including architecture and IP cores with Simulink and SoC Blockset library blocks. Then, use the SoC Builder tool to guide you through the steps required to build hardware and software executables, load them on an SoC device, and execute.

For an example of using the SoC Builder tool, see Streaming Data from Hardware to Software.

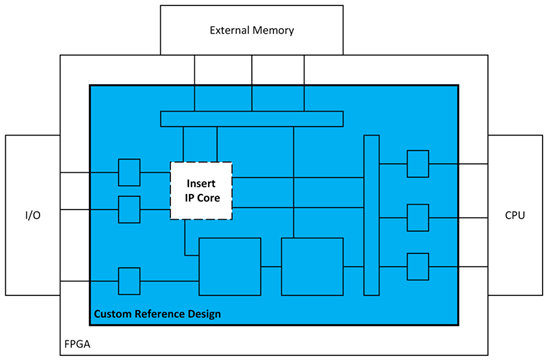

Export Reference Design Workflow

In this workflow, you design the system architecture with Simulink and SoC Blockset library blocks, leaving a place holder for the IP core. Use the socExportReferenceDesign function to generate a custom reference design

from the system architecture. Once generated, use this reference design as a fixed

reference design with the IP core generation workflow to integrate different IP cores,

and for algorithm development.

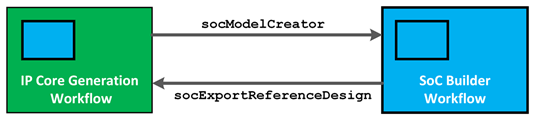

Transition Between Workflows

You can deploy an SoC model on an SoC device by using one of these workflows.

SoC Blockset provides these utility functions to transfer between workflows:

socExportReferenceDesign— Use this function to export a reference design from an SoC Blockset model. Then, integrate your IP core to the reference design and deploy it to an SoC device using the HDL Workflow Advisor tool.If you are authoring an IP core using the HDL Coder™ custom IP core generation workflow, you can create a custom reference design and integrate the IP core into that design. For an example of using the

socExportReferenceDesignfunction, see Export Custom Reference Design.SoC Model Creator — Use this tool to create an SoC model based on your selected reference design for the supported Xilinx® RFSoC or MPSoC devices. Use the created model as a template to design and simulate an FPGA algorithm and processor algorithm. Then, use the SoC Builder tool to generate a bitstream and host I/O model, build a software application, and program the Xilinx RFSoC or MPSoC device. For more information on this workflow, see Support for Fixed Reference Design. For supported devices, see Supported Xilinx Devices.

If you are designing an MPSoC or RFSoC application using a fixed reference design, open the SoC Model Creator tool first. If you are building an application based on the content in a Simulink model, you can use the RFSoC Template to get started quickly, or you can create the whole model from scratch.

These workflows require both SoC Blockset and HDL Coder products.