Deep Learning HDL Processing System

Libraries:

Description

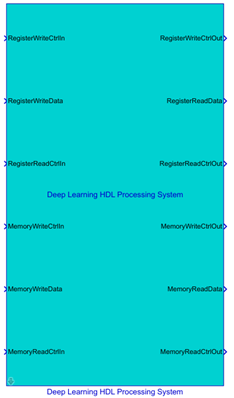

The Deep Learning HDL Processing System block simulates the deep learning

processor IP core and models, simulates, and validates the hand-shaking logic between the pre-

and post-processing systems and the deep learning processor IP core. The block icon changes

depending on the RunTimeControl property setting of the

dlhdl.ProcessorConfig object. To access the block at the MATLAB® command line,

enter:

open_system('dlhdlsim')RunTimeControl Setting | Block Icon |

|---|---|

Register |  |

Port |  |

Examples

Deploy and Verify YOLO v2 Vehicle Detector on FPGA

Deploy a you only look once (YOLO) v2 vehicle detector on FPGA and verify the end-to-end application using MATLAB.

(Vision HDL Toolbox)

Limitations

Batch processing mode for the deep learning processor IP core is not supported for simulation.

The data type of the

dlhdl.ProcessorConfigdata type must be set tosingle. Theint8data type is not supported.The top-level properties of the

dlhdl.ProcessorConfigobject must all be set to"Port"or"Register". A mix of port and register parameter settings is not supported.Multiple input networks are not supported.

Ports

Input

Input write data control bus, specified as a bus. The bus control signals are of

type BusAXIWriteCtrlM2S and includes these signals:

| Signal Name | Data Type |

|---|---|

wr_addr | uint32 scalar |

wr_len | uint32 scalar |

wr_valid | Boolean scalar |

Data Types: BusAXIWriteCtrlM2S

Input data, specified as a scalar or vector.

Data Types: uint32

Input data read control bus, specified as a bus. The bus control signals are of

type BusAXIReadCtrlM2S and includes these signals:

| Signal Name | Data Type |

|---|---|

rd_addr | uint32 scalar |

rd_len | uint32 scalar |

rd_avalid | boolean scalar |

rd_dready | boolean scalar |

Data Types: BusAXIReadCtrlM2S

Input DDR memory write data control bus, specified as a bus. The bus control

signals are of type BusAXIWriteCtrlM2S and includes these

signals:

| Signal Name | Data Type |

|---|---|

wr_addr | uint32 scalar |

wr_len | uint32 scalar |

wr_valid | Boolean scalar |

Data Types: BusAXIWriteCtrlm2S

Input DDR memory data specified as a scalar or vector.

Data Types: ufix128

Input DDR memory read data control bus, specified as a bus. The bus data type is

BusAXIReadCtrlM2S and includes these signals:

| Signal Name | Data Type |

|---|---|

rd_addr | uint32 scalar |

rd_len | uint32 scalar |

rd_avalid | boolean scalar |

rd_dready | boolean scalar |

Data Types: BusAXIReadCtrlM2S

Data processing start signal, specified as a boolean.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: Boolean

Number of input data frames, specified as a int32

scalar.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: int32

Data streaming stop signal, specified as a boolean.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: Boolean

Next input frame ready signal, specified as a boolean.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: Boolean

Current output data read complete signal, specified as a boolean.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: Boolean

Output

Output data write control bus, returned as a bus. The bus control signals are of

type BusAXIWriteCtrlS2M and includes these signals:

| Signal Name | Data Type |

|---|---|

wr_ready | boolean scalar |

wr_complete | boolean scalar |

Data Types: BusAXIWriteCtrlS2M

Output data returned as a scalar or vector.

Data Types: uint32

Output data read control bus, returned as a bus. The bus control signals are of

type BusAXIReadCtrlS2M and includes these signals:

| Signal Name | Data Type |

|---|---|

rd_aready | boolean scalar |

rd_dvalid | boolean scalar |

Data Types: BusAXIReadCtrlS2M

Output DDR memory data write control bus, returned as a bus. The bus control

signals are of type BusAXIWriteCtrlS2M and includes these

signals:

| Signal Name | Data Type |

|---|---|

wr_ready | boolean scalar |

wr_complete | boolean scalar |

Data Types: BusAXIWriteCtrlS2M

Output DDR memory data returned as a scalar or vector.

Data Types: ufix128

Output DDR memory data read control bus, returned as a bus. The bus control

signals are of type BusAXIReadCtrlS2M and includes these

signals:

| Signal Name | Data Type |

|---|---|

rd_aready | boolean scalar |

rd_dvalid | boolean scalar |

Data Types: BusAXIReadCtrlS2M

Input data memory address signal returned, as a uint32

scalar.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: uint32

Size of next input data frame, returned as a uint32 scalar. The

input data frame size is measured in bytes.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: uint32

Input data valid signal, returned as a boolean.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: Boolean

Processed output data memory address signal, returned as a

uint32 scalar.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: uint32

Size of next output data frame signal, returned as a uint32

scalar. Use this signal when the OutputValid signal is on.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: uint32

Output data valid signal, returned as a boolean scalar.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: Boolean

Data processing complete signal, returned as a boolean scalar.

Dependencies

To enable this port, set the RunTimeControl property of the

dlhdl.ProcessorConfig object to "port".

Data Types: Boolean

Parameters

Name of network object, specified as one of these options:

Network from MATLAB function— Provide the name of the MATLAB function that returns a network object.Network from MAT-file— Provide the path to the MAT-file that stores the network object.

Name of the MATLAB function that returns a network object.

Dependencies

To enable this parameter, set Network to

Network from MATLAB function.

Path to MAT-file that contains the network object.

Dependencies

To enable this parameter, set Network to

Network from MAT-file.

Name of network activation layer to simulate. The default activation layer is the last layer of the network object specified by the Network parameter.

Maximum input frame number limit to calculate DDR memory access allocation.

Processor Configuration Properties

Import an existing dlhdl.ProcessorConfig object. if you specify

a function name, it must be a MATLAB function. For example, this MATLAB function returns a dlhdl.ProcessorConfig object called

hPCinMATLAB.

function hPCinMATLAB = hPCinMATLAB() hPC = dlhdl.ProcessorConfig; hPC.RunTimeControl = "port"; hPCinMATLAB = hPC; end

After you add the MATLAB function name or dlhdl.ProcessorConfig object, click

Apply to import the processor configuration or MATLAB configuration into the block.

Export a dlhdl.ProcessorConfig object. The default object name

is hPCInSimulink.

Convolution Module

Enable or disable convolution module generation. Use this parameter to control generation of the convolution module as a part of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Enable or disable LRN block generation. Use this parameter to control generation of the LRN block as a part of the convolution module of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Enable or disable segmentation block generation. Use this parameter to control generation of the segmentation block as a part of the convolution module of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Number of parallel convolution processor kernel threads.

This parameter is the number of parallel 3-by-3 convolution kernel threads that

are a part of the conv module in the

dlhdl.ProcessorConfig object. To set the

ConvThreadNumber to 81, 100, 121, 144, 169, 196, 225, or 256

the ProcessorDataType parameter must be set to

int8 data type.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

This parameter is read-only.

Input memory cache BRAM size. This parameter is a 3-D matrix that represents the

maximum input image size permitted by the BRAM of the conv module

in the dlhdl.ProcessorConfig object.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Output memory cache BRAM size.

This parameter is a 3-D matrix that represents the maximum output image size

permitted by the BRAM of the conv module in the

dlhdl.ProcessorConfig object.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Maximum input and output feature size.

This parameter is a positive integer that represents the maximum input and output

feature size as a part of the conv module in the

dlhdl.ProcessorConfig object.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

FC Module

Enable or disable fully connected module generation. Use this parameter to control generation of the fully connected module as a part of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Enable or disable Softmax block generation. Use this parameter to control generation of the Softmax block as a part of the fully connected module of the deep learning processor configuration. When you clear this parameter, the Softmax layer is still implemented in software.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Number of parallel fully connected (FC) MAC threads. This parameter is the number

of parallel FC MAC threads that are a part of the fc module in the

dlhdl.ProcessorConfig object. To set the

FCThreadNumber to 32 or 64 the

ProcessorDataType parameter must be set to

int8 data type.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Input memory cache BRAM size. This parameter is an unsigned integer that

represents the input cache memory size permitted by the BRAM of the

fc module in the dlhdl.ProcessorConfig

object.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Output memory cache BRAM size. This parameter is an unsigned integer that

represents the output cache memory size permitted by the BRAM of the

fc module in the dlhdl.ProcessorConfig

object.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Custom Module

Enable or disable custom module generation. Use this parameter to control generation of the adder module as a part of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Enable or disable addition layer generation. Use this parameter to control generation of the addition layer as a part of the custom module of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Enable or disable multiplication layer generation. Use this parameter to control generation of the multiplication layer as a part of the custom module of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Enable or disable 2-D resize layer generation. Use this parameter to control generation of the 2-D resize layer as a part of the custom module of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Enable or disable sigmoid layer generation. Use this parameter to control generation of the sigmoid layer as a part of the custom module of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Enable or disable tanh layer generation. Use this parameter to

control generation of the tanh layer as a part of the custom module

of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Enable or disable mish layer generation. Use this parameter to

control generation of the mish layer as a part of the custom module

of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Enable or disable swish layer generation. Use this parameter to

control generation of the swish layer as a part of the custom

module of the deep learning processor configuration.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Input memory cache BRAM size. This parameter is an unsigned integer that

represents the input cache memory size permitted by the BRAM of the

custom module in the dlhdl.ProcessorConfig

object.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Output memory cache BRAM size. This parameter is an unsigned integer that

represents the input cache memory size permitted by the BRAM of the

custom module in the dlhdl.ProcessorConfig

object.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

Processor Top Level

This parameter is read-only.

Select the interface type for all deep learning processor IP core interface signals. Specify whether the run-time input signals, run-time feedback signals, input interface control input signals, and input interface control feedback signals are implemented as registers or ports.

Dependencies

To enable and edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

This parameter is read-only.

Deep learning processor IP core mode setting. Specify whether the run-time input signals to the deep learning processor IP core are implemented as registers or ports.

This parameter is read-only.

Feedback signals from deep learning processor IP core control. Specify whether the run-time output signals from the deep learning processor IP core are implemented as registers or ports.

This parameter is read-only.

Deep learning processor IP core input interface control.

This parameter is read-only.

Deep learning processor IP core output interface control.

This parameter is read-only.

Deep learning processor IP core user interface control.

Deep learning processor IP core module data type.

Dependencies

To edit this parameter, enable Export Processor Configuration to MATLAB Workspace.

This parameter is read-only.

Enable this option to export a structure containing address locations to the MATLAB workspace.

Version History

Introduced in R2023b

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)