複数のコイル間が相互結合している RLC ラダー回路網の入力アドミタンス応答

この例では、複数のコイル間が相互結合した RLC コンポーネントで構成される 4 セクション ラダー回路網をモデル化する方法を説明します。このラダー回路網の表現を使用して、変圧器のディスク巻線をモデル化できます。ラダー回路網のセクション数は、巻線内のディスク数で決まります。各セクションで、巻線内の 2 枚または 3 枚のディスクをモデル化できます。

各セクションの巻線抵抗と自己インダクタンスは Rs と Ls で表されます。直列静電容量 Cs と接地静電容量 Cg は、それぞれディスク間の静電容量と、巻線と接地間の静電容量をモデル化したものです。

この例では、各セクションは他の 3 セクションと相互に結合しています。Lumped Inductance ブロックまたは Distributed Inductance ブロックのいずれかを使用して、4 セクションのインダクタンスをモデル化し、相互インダクタンスを組み込むことができます。

相互インダクタンスを計算するには、各インダクタを他の 3 個のインダクタの入力端子に接続しなければなりません。Lumped Inductance ブロックは全セクションの総インダクタンスをモデル化するため、このブロックを使用して分岐のクラスタリングを最小限に抑えます。

Distributed Inductance ブロックは 4 個のインダクタをモデル化します。これらのブロックは 4 つの分岐電流の微分を物理量信号として受け取り、セクションの分岐電流の微分を出力します。

モデルを開く

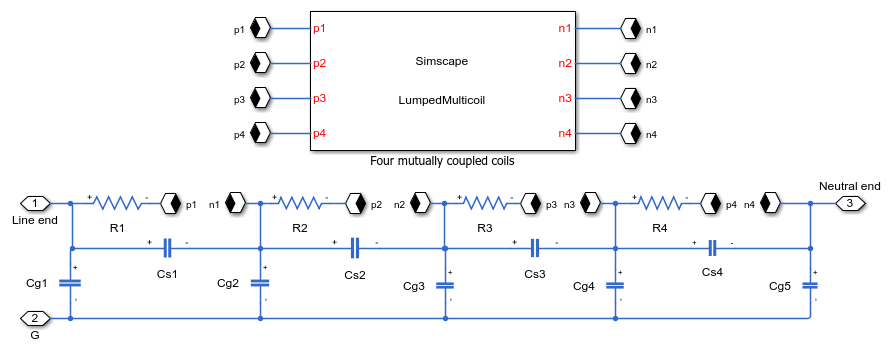

Lumped Inductance ブロックによるラダー回路網のモデル化

Lumped Inductance ブロックは、4 セクションの自己インダクタンス Ls と、各セクション間の相互インダクタンスをまとめてモデル化します。Lumped Inductance ブロックは、ブロック線図で p と n のラベルが付いている相接続と中性接続で構成されます。

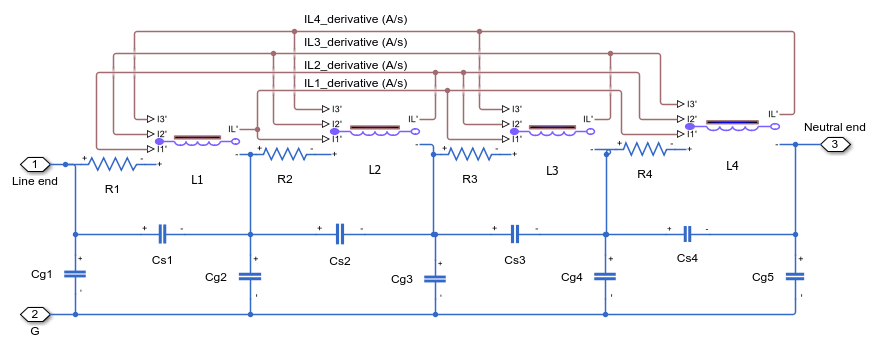

複数の Distributed Inductance ブロックによるラダー回路網のモデル化

各セクションは、他の 3 セクションからの分岐電流の微分を物理量信号として入力し、自らの分岐電流の微分を物理量信号として出力する Inductor ブロックで構成されます。

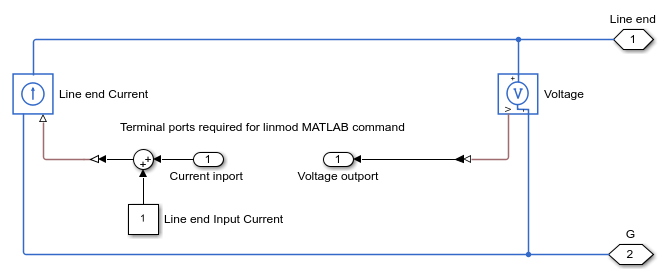

入力アドミタンス測定の設定

この例では、電圧センサーと制御電流源を介したラダー回路網の入力アドミタンス応答を推定します。Input Admittance Measurement Setup サブシステムが、システムの伝達関数を計算します。次に、アドミタンス応答が推定された伝達関数の逆数として計算されます。

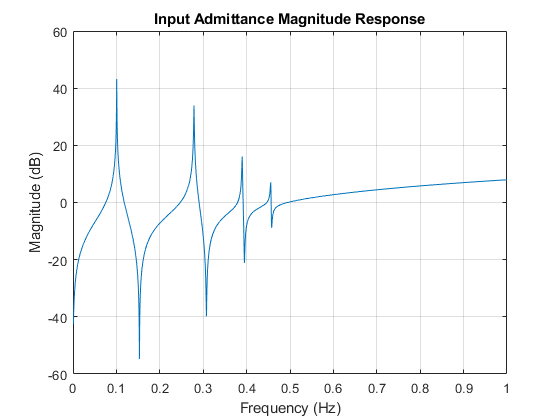

シミュレーション結果

以下のプロットは、4 セクション ラダー回路網の入力アドミタンスの振幅応答を示しています。

リアルタイム シミュレーションの結果

この例は、以下のプラットフォームでテストされました。

Intel® 3.5 GHz i7 マルチコア CPU と 4 GB の RAM を搭載した Speedgoat™ Performance リアルタイム ターゲット マシン。

3.5 GHz の Intel® Core XEON E3-1275v3 と 4 GB の RAM を搭載した dSPACE® SCALEXIO LabBox。

Simscape のローカル ソルバーを使用することで、このモデルを 5 マイクロ秒のステップ サイズでリアルタイム実行できます。サンプル レートが小さい場合、コールド キャッシュが原因で、最初のタスク実行中にタスク オーバーランが発生する可能性があります。このオーバーランを回避するには、選択したプラットフォームがこれらのオプションをサポートしている場合、タスク オーバーランの数を制限するか、リアルタイム アプリケーションの起動フェーズにおいてタスクのオーバーラン許容回数を制限するか、周期タスクのサンプル時間を延長することで、起動時の動作を緩和できます。