強調表示されたモデルの調整

モデル スライサーを使用してモデルを強調表示した後、モデル内で強調表示された部分の依存関係のパスを調整できます。モデル スライサーによって強調表示されたモデルを調整すると、指定したシミュレーション時間枠の一部で使用されたブロックだけが含まれるようにしたり、ブロックまたは Switch ブロックの特定の入力を除外することができます。モデル内の強調表示された部分を調整することで、モデルに関連する部分のみを含められます。

シミュレーション時間枠の定義

指定したシミュレーション時間枠で使用されたブロックのみを含めるよう、強調表示されたモデルを調整できます。シミュレーション時間枠を定義すると、いくつかの Switch ブロックが一定に保たれ、結果として非アクティブな入力が削除されます。

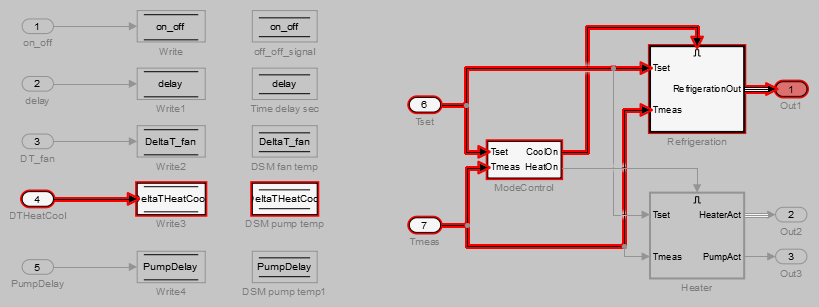

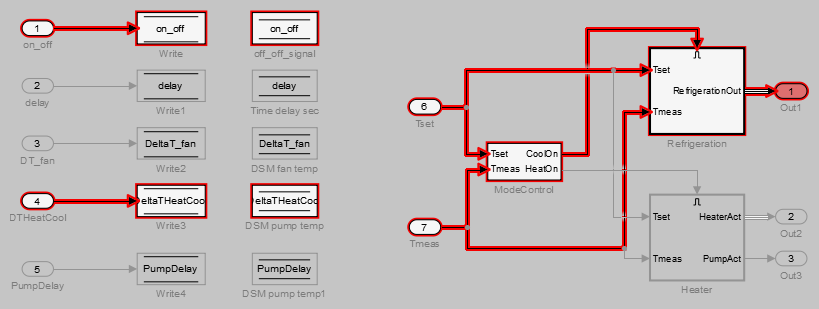

1.sldvSliceClimateControlExample モデルを開きます。

open_system("sldvSliceClimateControlExample");2.[モデルの検証、妥当性確認、テスト] ギャラリーの下の [アプリ] タブで、[モデル スライサー] をクリックします。

モデル スライサーを開くと、モデル スライサーはモデルをコンパイルします。その後、モデル スライスのプロパティを設定します。

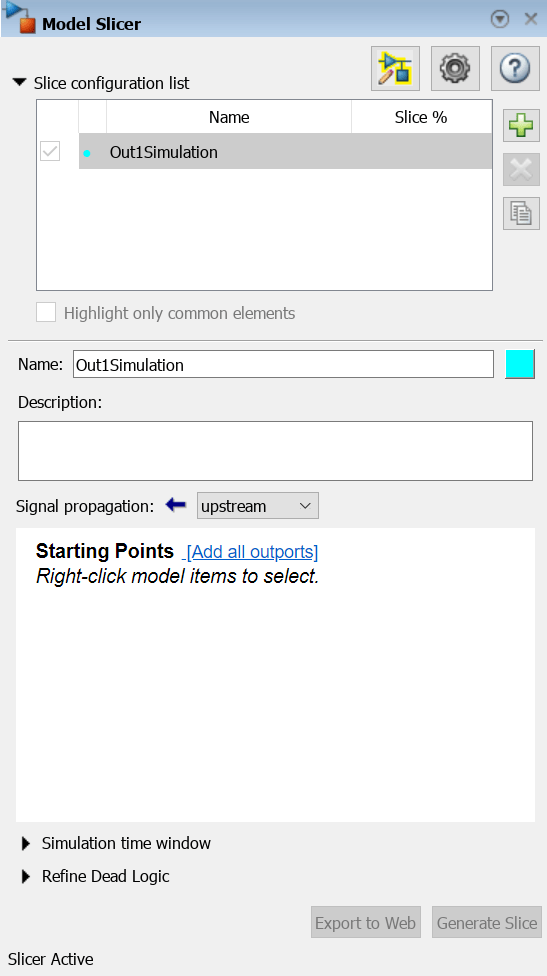

3.モデル スライサーで、矢印をクリックして [スライス構成リスト] を展開します。

4.スライスのプロパティを設定します。

(a) 名前: Out1Simulation

(b) 色: ![]() (シアン)

(シアン)

(c) 信号伝播: 上流

5.モデルの最上位レベルで、スライスの開始点として Out1 ブロックを選択します。Out1 ブロックを右クリックし、[モデル スライサー]、[開始点として追加] を選択します。

モデルが強調表示されます。

6.モデル スライサーで [シミュレーション時間枠] を選択します。

7.シミュレーション時間枠の終了時間を指定するには、モデル スライサーで [シミュレーションを実行] ボタン ![]() をクリックします。

をクリックします。

8.[終了時間] を 10 に設定します。

9.[OK] をクリックしてシミュレーションを開始します。

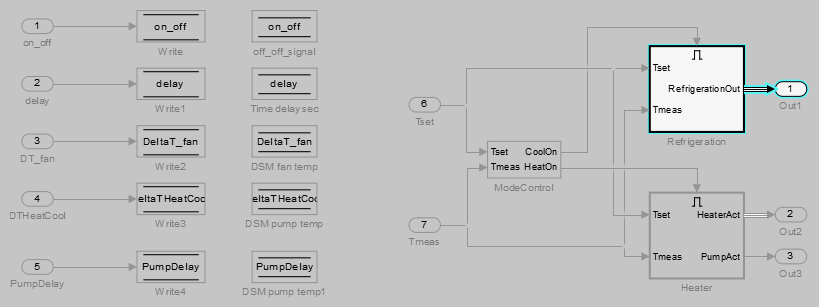

入力した終了時間まで、アクティブなブロックのみにパスが制限されます。

10.[終了時間] を 5 に設定し、定義したシミュレーション時間枠のモデルを強調表示します。[強調] をクリックします。

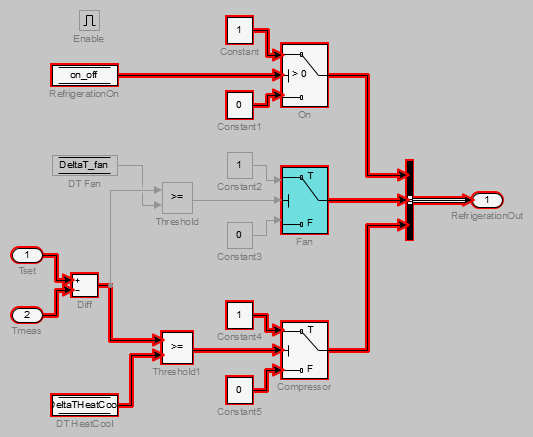

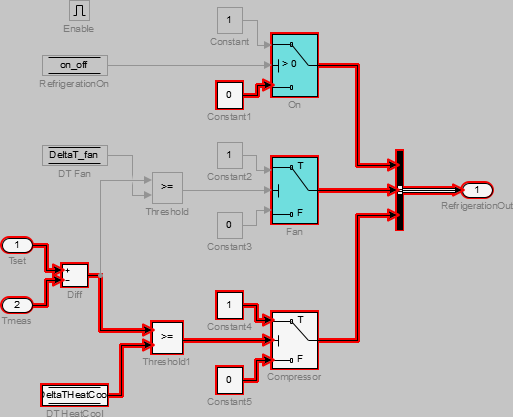

11.この制約がモデル内の強調表示された部分にどのように影響するか確認するには、Refrigeration サブシステムを開きます。

モデル内の強調表示された部分には、指定したシミュレーション時間枠内でアクティブなスイッチの入力端子のみが含まれます。

指定したシミュレーション時間枠の一部で使用されたブロックのみが含まれるように強調表示されたモデルを調整した後、モデル内の強調表示された部分を組み込んでスタンドアロンの簡略化モデルの作成を実行できます。

ブロックの除外

解析からブロックが除外されるよう、強調表示されたモデルを調整できます。ブロックを除外すると、依存関係の伝播が停止するため、除外されたブロックより後の解析方向にある信号およびモデル項目は無視されます。

除外点は簡略化されたモデルの依存関係を参照するのに便利です。たとえば、フィードバック パスを制御すると、依存関係が幅広く形成され、強調表示されるモデルの領域がより広範囲になります。フィードバック パスをもつモデルの場合では特に、除外点を使用することで解析を制限できます。

メモ

スタンドアロンの簡略化モデルの作成は、強調表示されたモデルに除外点が含まれる場合、サポートされません。

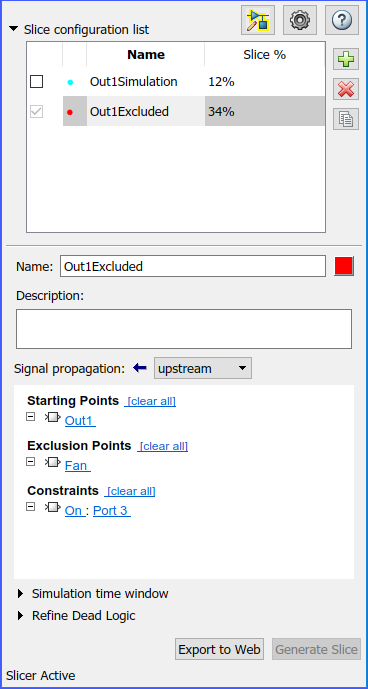

モデル スライサーで、矢印をクリックして [スライス構成リスト] を展開します。

新しいスライス構成を追加するには、[新規追加] ボタン

をクリックします。

をクリックします。スライスのプロパティを設定します。

名前:

Out1Excluded色:

(レッド)

(レッド)信号伝播:

上流

モデルの最上位レベルで、スライスの開始点として

Out1ブロックを選択します。Out1ブロックを右クリックし、[モデル スライサー]、[開始点として追加] を選択します。

モデルが強調表示されます。

Refrigerationをダブルクリックしてサブシステムを開きます。FanSwitch ブロックを右クリックしてから [モデル スライサー]、[除外点として追加] を選択します。FanSwitch ブロックの上流のみにあるブロックは強調表示されなくなります。DT FanData Store Read ブロックは強調表示されなくなります。

この制約がモデルの強調表示された部分にどのように影響するか確認するには、親システムを参照します。

DSM fan tempData Store Memory ブロックおよびWrite2Data Store Write ブロックは、Refrigerationサブシステム内のDT FanData Store Read のアクセス先でなくなるため、強調表示されなくなります。

Switch ブロックの入力の除外

信号の経路指定が複雑な場合、Switch ブロックを経由して依存関係の分析パスを利用可能なパスのサブセットに制約できます。制約はモデル スライサーに表示されます。

メモ

スタンドアロンの簡略化モデルの作成は、制約された Switch ブロックを含む強調表示されたモデルではサポートされません。

Refrigerationをダブルクリックしてサブシステムを開きます。OnSwitch ブロックを制約します。Switch ブロックを右クリックし、[モデル スライサー]、[制約の追加] を選択します。

[制約] ダイアログ ボックスで [Port 3] を選択します。

[OK] をクリックします。

パスはスイッチの

Constant1端子に制限されます。制約されたスイッチの [Port 1] および [Port 2] より上流にあるブロックは強調表示されなくなります。[Port 3] より上流のブロックのみ強調表示されます。

この制約がモデルの強調表示された部分にどのように影響するか確認するには、親システムを参照します。