Improving Filter Performance with Pipelining

Optimizing the Clock Rate with Pipeline Registers

You can optimize the clock rate used by filter code by applying pipeline registers. Although the registers increase the overall filter latency and space used, they provide significant improvements to the clock rate. These registers are disabled by default. When you enable them, the coder adds registers between stages of computation in a filter.

| For... | Pipeline Registers Are Added |

|---|---|

| FIR, antisymmetric FIR, and symmetric FIR filters | Between levels of the final summation tree |

| Transposed FIR filters | Between coefficient multipliers and adders |

| IIR filters | Between sections |

| CIC | Between comb sections |

For example, for a sixth order IIR filter, the coder adds two pipeline registers. The coder inserts a pipeline register between the first and second section, and between the second and third section.

For FIR filters, the use of pipeline registers optimizes filter final summation. For details, see Optimizing Final Summation for FIR Filters.

Note

Pipeline registers in FIR, antisymmetric FIR, and symmetric FIR filters can produce numeric results that differ from the results produced by the original filter object, because they force the tree mode of final summation.

To use pipeline registers,

Select the Add pipeline registers option in the Filter architecture pane of the Generate HDL tool.

For FIR, antisymmetric FIR, and symmetric FIR filters, consider setting an error margin for the generated test bench to account for numeric differences. The error margin is the number of least significant bits the test bench ignores when comparing the results. To set an error margin:

Select the Test Bench pane in the Generate HDL tool. Then click the Configuration tab.

Set the Error margin (bits) field to an integer that indicates the maximum acceptable number of bits of difference in the numeric results.

Continue setting other options or click Generate to initiate code generation.

Command-Line Alternative: Use the generatehdl function with the property AddPipelineRegisters

to optimize the filters with pipeline registers.

Multiplier Input and Output Pipelining for FIR Filters

If you retain multiplier operations for a FIR filter, you can achieve higher clock rates by adding pipeline stages at multiplier inputs or outputs.

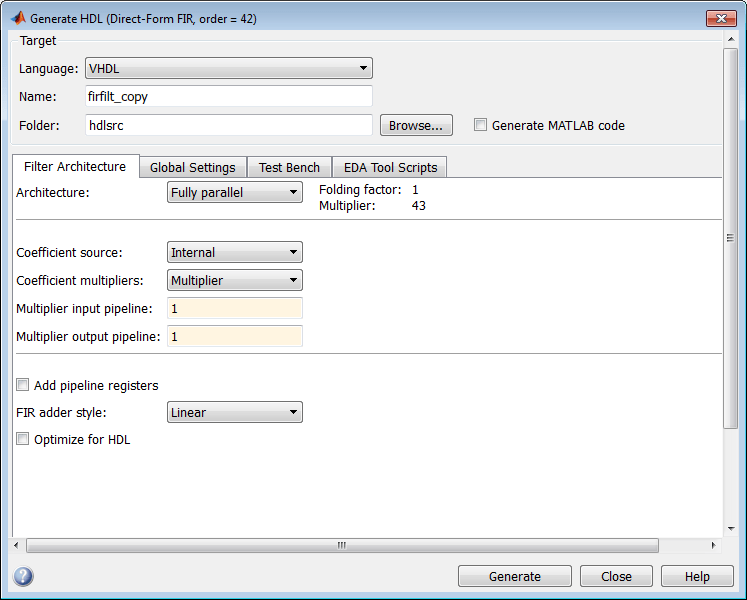

This figure shows the UI options for multiplier pipelining options. To enable these

options, Coefficient multipliers to

Multiplier.

Multiplier input pipeline: To add pipeline stages before each multiplier, enter the desired number of stages as an integer greater than or equal to

0.Multiplier output pipeline: To add pipeline stages after each multiplier, enter the desired number of stages as an integer greater than or equal to

0.

Command-Line Alternative: Use the generatehdl function with the MultiplierInputPipeline and MultiplierOutputPipeline properties to specify multiplier pipelining for FIR

filters.

Optimizing Final Summation for FIR Filters

If you are generating HDL code for an FIR filter, consider optimizing the final summation technique to be applied to the filter. By default, the coder applies linear adder summation, which is the final summation technique discussed in most DSP text books. Alternatively, you can instruct the coder to apply tree or pipeline final summation. When set to tree mode, the coder creates a final adder that performs pairwise addition on successive products that execute in parallel, rather than sequentially. Pipeline mode produces results similar to tree mode with the addition of a stage of pipeline registers after processing each level of the tree.

In comparison,

The number of adder operations for linear and tree mode are the same. The timing for tree mode can be better due to parallel additions.

Pipeline mode optimizes the clock rate, but increases the filter latency. The latency increases by

log2(number of products), rounded up to the nearest integer.Linear mode helps attain numeric accuracy in comparison to the original filter object. Tree and pipeline modes can produce numeric results that differ from the results produced by the filter object.

To change the final summation to be applied to an FIR filter:

Select one of these options in the Filter architecture pane of the Generate HDL tool.

For... Select... Linear mode (the default) Linearfrom the FIR adder style menuTree mode Treefrom the FIR adder style menuPipeline mode The Add pipeline registers check box If you specify tree or pipelined mode, consider setting an error margin for the generated test bench to account for numeric differences. The error margin is the number of least significant bits the test bench ignores when comparing the results. To set an error margin,

Select the Test Bench pane in the Generate HDL tool. Then click the Configuration tab.

Set the Error margin (bits) field to an integer that indicates the maximum acceptable number of bits of difference in the numeric results.

Continue setting other options or click Generate to initiate code generation.

Command-Line Alternative: Use the generatehdl function with the property FIRAdderStyle or AddPipelineRegisters

to optimize the final summation for FIR filters.

Specifying or Suppressing Registered Input and Output

The coder adds an extra input register (input_register) and an extra

output register (output_register) during HDL code generation. These extra

registers can be useful for timing purposes, but they add to the overall latency.

This process block writes to extra input register input_register when

a clock event occurs and clk is active high

(1):

Input_Register_Process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

input_register <= (OTHERS => '0');

ELSIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

input_register <= input_typeconvert;

END IF;

END IF;

END PROCESS Input_Register_Process ;

This process block writes to extra output register output_register

when a clock event occurs and clk is active high (1):

Output_Register_Process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

output_register <= (OTHERS => '0');

ELSIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

output_register <= output_typeconvert;

END IF;

END IF;

END PROCESS Output_Register_Process;

If overall latency is a concern for your application and you do not have timing requirements, you can suppress generation of the extra registers as follows:

Select the Global Settings tab on the Generate HDL tool.

Select the Ports tab in the Additional settings pane.

Clear Add input register and Add output register as required. This figure shows the setting for suppressing the generation of an extra input register.

Command-Line Alternative: Use the generatehdl and function with the properties AddInputRegister and

AddOutputRegister to add

an extra input or output register.