モデル化

ハードウェア接続用のモデルの準備、およびハードウェア プロトコルをサポートするためのブロックの追加

AMD® SoC デバイス用のブロックおよびシミュレーション機能。

ブロック

| AXI4-Interface Read | Read data from IP core on AMD SoC Device |

| AXI4-Interface Write | Write data to IP core on AMD SoC Device |

| Linux Task | Spawn task function as separate Linux thread |

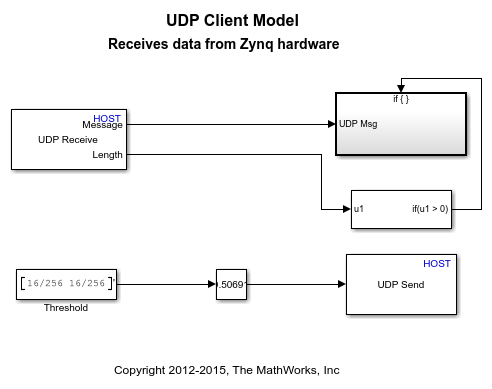

| UDP Receive | UDP データを受信 |

| UDP Send | UDP メッセージを送信 |

| VxWorks Task | タスク関数を別の VxWorks スレッドとして発生させる |

| AXI4-Stream IIO Write | Write AXI4-Stream Data using IIO |

| AXI4-Stream IIO Read | Read AXI4-Stream Data using IIO |

関数

zynqlib | Open the Simulink Library Browser to the Embedded Coder Support Package for AMD SoC Devices block library |