このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

シミュレーションのタイムスケール

シミュレーション時間の表現の概要

シミュレーション時間の表現は、HDL シミュレータとSimulink®の間で大きく異なります。各アプリケーションには独自のタイミング エンジンがあり、検証ソフトウェアは 2 つのアプリケーション間のシミュレーション時間を同期する必要があります。

HDL シミュレーターでは、シミュレーション時間の単位は「ティック」と呼ばれます。ティックの長さは、HDL シミュレーターの「解像度制限」によって定義されます。デフォルトの分解能制限は 1 ns ですが、シミュレータによって異なる場合があります。

ModelSim®ユーザー:

現在のModelSim の解像度制限を確認するには、

echo $resolutionreport simulator stateを入力します。デフォルトの解像度制限をオーバーライドするには、ModelSimオプションを指定するか、 ModelSimで別のシミュレータ解像度を選択します。 $$シミュレーション ダイアログ ボックス。ModelSimで使用可能な解像度は、fs、ps、ns、us、ms、または sec の単位で 1x、10x、または 100x です。詳細については、ModelSimのドキュメントを参照してください。Xcelium™ユーザー:

現在の HDL シミュレータの解像度制限を確認するには、HDL シミュレータ プロンプトで

echo $timescaleと入力します。詳細については、HDL シミュレータのドキュメントを参照してください。Vivado®ユーザー: HDL Cosimulationブロック マスクを開きます。HDL Time Precisionパラメーターの値は、「Block Info」タブで確認できます。この値を変更するには、コシミュレーション ウィザード を開き、 HDL time precisionパラメーターを指定してブロックを再生成する必要があります。

Simulink は、シミュレーション時間を秒単位の倍精度値として維持します。この表現は、連続システムと離散システムの両方のモデリングに対応します。

Simulinkと HDL シミュレーターのタイミングの関係は、シミュレーションの次の側面に影響します。

合計シミュレーション時間

入力ポートのサンプル時間

出力ポートのサンプル時間

クロック周期

シミュレーションの実行中、 Simulink は、各中間ステップで現在のシミュレーション時間を HDL シミュレーターに通信します。(中間ステップは、Simulinkサンプル時間のヒットに対応します。各中間ステップで、新しい値が入力ポートに適用されるか、出力ポートがサンプリングされます。)

コシミュレーション中に HDL シミュレータをSimulinkで最新の状態にするには、サンプリングされたSimulink時間を HDL シミュレータ時間 (ティック) に変換し、HDL シミュレータが計算されたティック数の間実行されます。

Simulinkと HDL シミュレータのタイミング関係の定義

シミュレーション時間の表現の違いは、HDL Verifier™インターフェイスを使用する 2 つの方法のいずれかで調整できます。

タイミング関係を手動で定義する ( Timescalesペインを使用)

関係を手動で定義する場合は、 HDL シミュレーターでSimulinkの 1 秒を何フェムト秒、ピコ秒、ナノ秒、マイクロ秒、ミリ秒、秒、またはティックで表すかを決定します。

HDL Verifier でタイムスケールを定義できるようにする ( Timescalesペインを使用)

ソフトウェアにタイミング関係の定義を許可すると、HDL シミュレータとSimulinkの間のタイムスケール係数が、HDL シミュレータの 1 秒 = TGの 1 秒にできるだけ近くなるように設定しようとします。 Simulink。この設定が不可能な場合、 HDL Verifierは、 Simulinkモデル ポートの信号レートを可能な限り低い HDL シミュレータ ティック数に設定しようとします。

HDL Verifierによるタイミングモードの設定

HDL Cosimulation ブロックパラメーターダイアログ ボックスのHDL Cosimulation Timescalesペインは、1 秒のSimulink時間と一定量の HDL シミュレーター時間の間の対応を定義します。 。この HDL シミュレータ時間は、次のいずれかの方法で表現できます。

「相対的」な条件で (つまり、HDL シミュレータのティック数として)。この場合、協調シミュレーションは「相対タイミング モード」で動作すると言われます。HDL Cosimulation ブロックは、デフォルトで相互シミュレーションの相対タイミング モードに設定されます。相対タイミング モードの詳細については、 相対タイミングモードを参照してください。

「絶対」単位(ミリ秒やナノ秒など)。この場合、協調シミュレーションは「絶対タイミング モード」で動作すると言われます。絶対タイミング モードの詳細については、 「絶対タイミングモード」を参照してください。

Timescalesペインでは、同等の HDL シミュレーターを入力するか、 を指定することにより、 HDL VerifierSimulinkと HDL シミュレーターの間の最適なタイミング関係を選択できます。はタイムスケールを計算します。

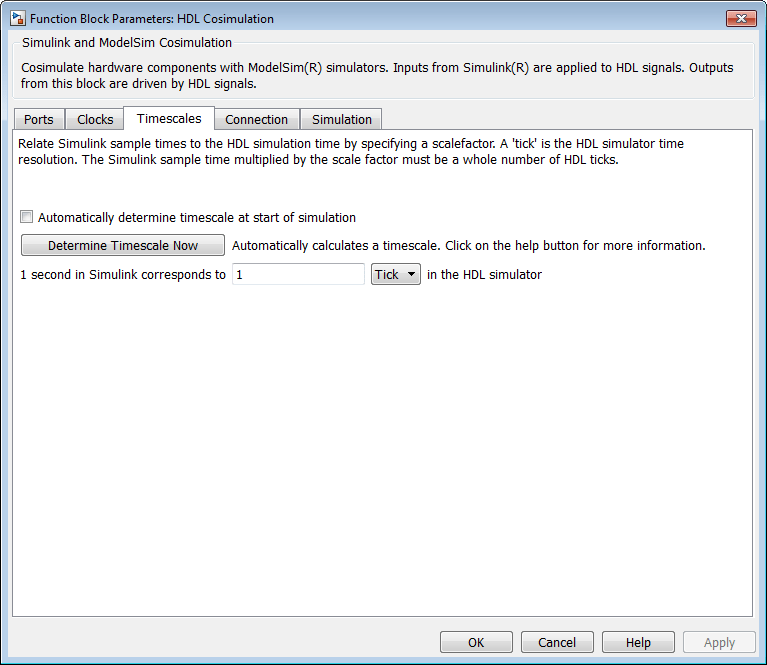

ブロック ダイアログでパラメータを設定しているときに、 HDL Verifier Timescaleオプションをクリックしてから Determine Timescale Now をクリックすると、 Determine Timescale Nowでタイムスケールを計算するように選択パラメーター。 $ (このパラメーターはShow Times and Suggest Timescaleに対してVivadoとして表示されます)、またはを選択して、シミュレーション開始時のタイムスケールをHDL Verifierに計算させることもできます。 Automatically determine timescale at start of simulation。

次の図は、 Timescalesペインのデフォルト設定を示しています (示されている例はModelSimで使用するものです)。

手動またはTimescalesダイアログ ボックスを使用してタイミング モードを設定する手順については、 Timescalesブロック リファレンスのHDL Cosimulationペインを参照してください。

タイミング関係を自動的に指定

HDL Verifierソフトウェアにタイミング関係を計算させるには:

HDLシミュレーターを起動します。 HDL Verifierソフトウェアは、HDL シミュレーターが実行されている場合にのみ、HDL シミュレーターの解像度制限を取得できます。

HDL Verifierソフトウェアにタイムスケールを即座に提案させるか、 Simulinkシミュレーションの開始時にタイムスケールを計算するかを選択します。

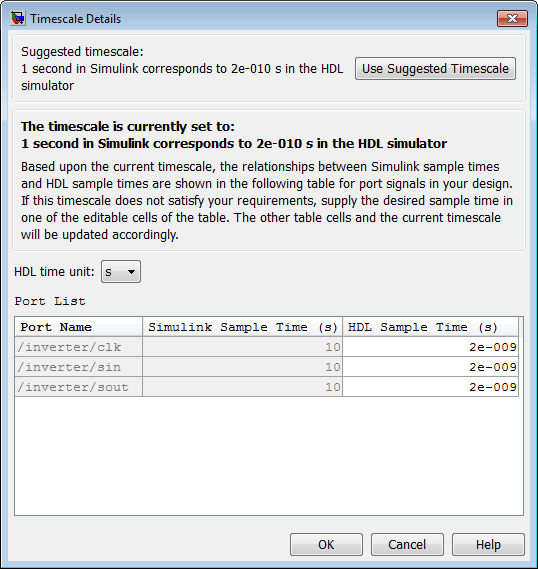

ブロックの構成中に計算を実行するには、 [Timescale]タブでDetermine Timescale Nowをクリックします。ソフトウェアはSimulinkを HDL シミュレータに接続し、 Simulink がHDL シミュレータの解像度を使用して最適なタイムスケールを計算できるようにします。リンクにより、それらの結果がTimescale Detailsダイアログ ボックスに表示されます。

提案されたタイムスケールを受け入れることも、ポート リストを直接変更することもできます。

最初に計算された設定に戻すには、 Use Suggested Timescaleをクリックします。

HDL デザインのすべてのポートのサンプル時間を表示するには、 Show all ports and clocksを選択します。

シミュレーションの開始時に計算を実行するには、 Automatically determine timescale at start of simulationを選択し、 Applyをクリックします。Timescale Detailsでシミュレーションを開始すると、同じSimulink ダイアログ ボックスが表示されます。

結果を表示するには、HDL シミュレーターが実行中であり、デザインが協調シミュレーション用にロードされていることを確認してください。シミュレーションを実行している必要はありません。

HDL Verifierソフトウェアは、スケール ファクターを計算するときに、HDL Cosimulation ブロックからのすべてのクロックおよびポート信号レートを分析します。

リンク ソフトウェアは、秒またはティックのいずれかでサンプル レートを返します。

結果が秒単位の場合、リンク ソフトウェアは忠実度 (絶対時間) を優先してタイミングの違いを解決できたことになります。

結果がティック単位である場合、リンク ソフトウェアは効率 (相対時間) を優先してタイミングの違いを最もよく解決できたことになります。

Determine Timescale NowまたはAutomatically determine timescale at start of simulationを選択するたびに、対話型表示が開きます。この表示では、タイムスケールの計算結果が説明されます。リンク ソフトウェアが指定されたサンプル時間のタイムスケールを計算できない場合は、 Port Listでサンプル時間を調整します。

「Apply」をクリックして変更をコミットします。

制限

HDL Verifier は、フレームベースの信号から自動的に計算されるタイムスケールをサポートしません。

HDL Verifierソフトウェアは、Tcl コマンドまたは HDL シミュレータで駆動される信号に基づいてサンプル タイムスケールを自動的に計算できません。リンク ソフトウェアはこれらの信号のレートを知ることができないため、そのような計算を実行できません。

結果を表示するには、HDL シミュレーターが実行中であり、デザインが協調シミュレーション用にロードされていることを確認してください。シミュレーションを実行している必要はありません。

相対タイミングモード

相対タイミング モードでは、Simulinkのシミュレーション時間と HDL シミュレーターの間の次の 1 対 1 の対応を定義します。

Simulinkの 1 秒 は、HDL シミュレータの N ティック に対応します。TG Nはスケール係数です。 |

この対応関係は、HDL シミュレータのタイミング解像度に関係なく当てはまります。

次の疑似コードは、Simulink時間単位が HDL シミュレータ ティックにどのように変換されるかを示しています。

InTicks = N * tInSecs

ここで、 InTicksは HDL シミュレータ時間 (ティック単位)、 tInSecsはSimulink時間 (秒単位)、 Nはスケール係数です。

相対タイミングモードの動作

HDL Cosimulationブロックのデフォルトは相対タイミング モードで、スケール ファクターは 1 です。したがって、1 Simulink秒は、HDL シミュレータの 1 ティックに対応します。デフォルトの場合:

Simulinkの合計シミュレーション時間が

N秒として指定されている場合、HDL シミュレーションは正確にNティックの間実行されます (つまり、Nns(デフォルトの解像度制限)。同様に、 SimulinkがHDL Cosimulationブロック入力端子のサンプル時間を Tsi 秒として計算すると、新しい値が正確な倍数で HDL 入力端子に格納されます。 Tsi カチカチ。出力ポートに明示的に指定されたサンプル時間が Tso 秒である場合、値は Tso ティックの倍数で HDL シミュレーターから読み取られます。

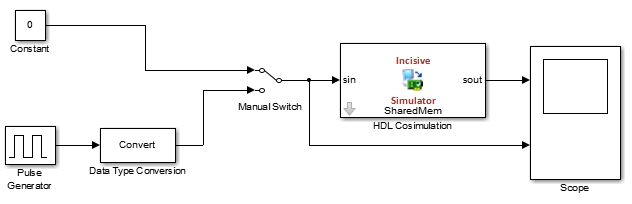

相対タイミングモードの例

相対タイミング モードがどのように動作するかを理解するには、次のモデル例からの協調シミュレーション結果を確認してください。

絶対タイミングモード

絶対タイミング モードでは、 Simulinkと HDL シミュレータの間のタイミング関係を絶対時間単位とスケール ファクタで定義できます。

| Simulinkの 1 秒 は、HDL シミュレータの (N * Tu) 秒 に対応します。ここで、Tu は絶対時間単位 (たとえば、ms、ns など) であり、 N はスケール係数です。 |

絶対タイミング モードでは、 Simulinkのすべてのサンプル時間とクロック周期が HDL シミュレータ ティックに量子化されます。次の疑似コードは変換を示しています。

tInTicks = tInSecs * (tScale / tRL)

ここで、

tInTicksは、ティック単位の HDL シミュレーター時間です。tInSecsは、 Simulink時間 (秒) です。tScaleは、 Timescales HDL Cosimulation ペインで選択されたタイムスケール設定 (単位とスケール係数) です。tRLは、 HDL シミュレーターの解像度制限です。

たとえば、 Timescalesペイン設定が 1 秒、HDL シミュレーターの解像度制限が 1 ns の場合、12 ns の出力ポートのサンプル時間は次のようにティックに変換されます。

tInTicks = 12ns * (1s / 1ns) = 12

アブソリュートタイミングモードの動作

絶対タイミング モードのタイムスケールパラメーターを設定するには、 Tickを選択するのではなく、 Simulink秒に対応する絶対時間の単位を選択します。

絶対タイミングモードの例

絶対タイミング モードの動作を理解するために、 相対タイミングモードの動作で説明したサンプル モデルを再度検討します。モデルが次のように再構成されたとします。

Simulinkのシミュレーションパラメーター:

Timescaleパラメーター:

1 sSimulink は、HDL シミュレータ時間の1 sに対応します。合計シミュレーション時間:

60e-9 s (60ns)入力ポート (

/inverter/inport) サンプル時間:24e-9 s (24 ns)出力ポート (

/inverter/outport) サンプル時間:12e-9 s (12 ns)クロック (

inverter/clk) 周期:10e-9 s (10 ns)

HDL シミュレーターの解像度制限:

1 ns

これらのシミュレーションパラメーターを指定すると、 Simulinkソフトウェアは HDL シミュレーターと 60 ns 間協調シミュレーションを行い、その間Simulink は24 ns の間隔で入力をサンプリングし、出力を 24 ns の間隔で更新します。 12ns 間隔でクロックを駆動し、10ns 間隔でクロックを駆動します。

次の図は、コシミュレーション実行後のModelSim waveウィンドウを示しています。

タイミング モードの使用上の考慮事項

タイムスケール モードを設定するときは、次の考慮事項に基づいて設定を選択する必要がある場合があります。

タイミングモードの使用制限

絶対タイミング モードと相対タイミング モードの使用には、次の制限が適用されます。

モデル内の複数のHDL Cosimulationブロックが HDL シミュレーターの単一インスタンスと通信している場合、すべてのHDL Cosimulationブロックは同じTimescalesを持つ必要があります。ペインの設定。

連続したコシミュレーション実行の間にHDL Cosimulation Timescalesペイン設定を変更した場合は、HDL シミュレータでシミュレーションを再起動する必要があります。

HDL ティックの整数として表現できないSimulinkサンプル時間を指定すると、エラーが発生します。

非整数の期間

非整数の期間を使用する場合、HDL シミュレーターはそのような無限に繰り返される値を表すことができません。したがって、シミュレーターは期間を切り捨てますが、その方法はSimulinkが値を切り捨てる方法とは異なるため、2 つの期間は一致しなくなります。

次の例は、次のシナリオでタイミング関係を設定する方法を示しています。非整数の期間に対応するのサンプル期間Simulinkを使用したいとします。 。

ここでの重要な考え方は、 Simulink時間を常に HDL ティックと関連付けることができなければならないということです。HDL ティックは、HDL シミュレータが認識する最も細かいタイム スライスです。 ModelSimの場合、デフォルトのティックは 1 ns ですが、1 fs までの精度にすることができます。

ただし、3 Hz 信号の実際の周期は 333.33333333333... ms であり、これは HDL シミュレータにとって有効なティック周期ではありません。HDL シミュレーターはそのような数値を切り捨てます。しかし、 Simulink は同じ決定を下しません。したがって、2 つの独立したシミュレーターの同期を維持しようとする協調シミュレーションの場合は、何も仮定する必要はありません。代わりに、数値を切り捨てるのが便利か四捨五入するのが便利かを決定する必要があります。

したがって、解決策は、Simulinkサンプル時間または HDL サンプル時間 (タイムスケール経由) を有効な数値に「スナップ」することです。可能性は無限にありますが、スナップを実行するいくつかの方法を次に示します。

Simulinkサンプル時間を 1/3 秒から 0.33333 秒に変更し、コシミュレーション ブロックのタイムスケールを「 Simulinkで 1 秒 = HDL シミュレータで 1 秒」に設定します。HDL CosimulationブロックClocksペインでクロックを指定する場合、その周期は 0.33333 秒である必要があります。

Simulink のサンプル時間を 1/3 秒に保ちます。 HDL シミュレータではSimulink = 6 ティックで 1 秒です。

HDL CosimulationブロックClocksペインでクロックを指定する場合、その周期は 1/3 である必要があります。簡単に言えば、この仕様はSimulinkに対し、HDL 時間分解能に関係なく、各Simulinkサンプル時間を (1/3*6) = 2 ティックごとに対応させるように指示します。

デフォルトの HDL シミュレーターの解像度が 1 ns の場合、HDL サンプル時間は 2 ns ごとであることを意味します。このサンプル時間は、 Simulinkサンプル時間ごとに対応する HDL サンプル時間が存在するように機能します。

ただし、 Simulink は1/3 秒の周期で考え、HDL は 2 ns の周期で考えます。したがって、デバッグ中に混乱する可能性があります。これを実際の周期 (5 桁、つまり 333.33 ミリ秒など) に一致させたい場合は、リストされている次のオプションに従うことができます。

HDL シミュレータでは、Simulinkサンプル時間をSimulink = 0.99999e9 ティックで 1/3 秒と 1 秒に保ちます。HDL CosimulationブロックClocksペインでクロックを指定する場合、その周期は 1/3 である必要があります。

HDL Cosimulationブロック ポートのサンプル時間の設定

一般に、 Simulink は、 HDL Cosimulationブロックの端子のサンプル時間を次のように処理します。

入力ポートが順伝播に基づいて明示的なサンプル時間を持つ信号に接続されている場合、 Simulinkはそのレートをその入力ポートに適用します。

入力ポートが明示的なサンプル時間を「持たない」信号に接続されている場合、 Simulink は、識別されたすべての入力ポート サンプルの最小公倍数 (LCM) に等しいサンプル時間を割り当てます。モデルの場合。

Simulink は入力ポートのサンプル期間を設定した後、ユーザー指定の出力サンプル時間をすべての出力ポートに適用します。サンプル時間はすべての出力ポートに対して明示的に定義する必要があります。

「相対」タイミング モードで協調シミュレーション用のモデルを開発している場合は、次のサンプル時間ガイドラインを考慮してください。

HDL Cosimulationブロックの出力サンプル時間を、HDL シミュレーターで定義された解像度制限の整数倍として指定します。HDL シミュレータ コマンドreport simulator stateを使用して、ロードされたモデルの解像度制限を確認します。HDL シミュレーターの解像度制限が 1 ns で、ブロックの出力サンプル時間を 20 に指定した場合、 Simulink は20 ns ごとに HDL シミュレーターと対話します。 |