最適化の基礎

階層のフラット化、遅延の均衡化、検証モデル、制限付きオーバークロック、フィードバック ループの強調表示

階層のフラット化、遅延の均衡化、フィードバック ループの強調表示などの最適化を適用することで、ターゲットの FPGA または SoC デバイスに合わせて設計を最適化します。基礎となる最適化を適用すると、よりハードウェア効率に優れた HDL コードを生成し、生成されたコードを適切にシミュレートするのに役立ちます。

チェック

トピック

- HDL Coder での速度および面積の最適化

さまざまな速度および面積の最適化と、設計の最適化方法を確認。

- フィードバック ループの検出

最適化を抑制するフィードバック ループの強調表示

- 階層のフラット化

面積と速度の最適化を拡張するためにサブシステム階層をフラットにします。

- 制限付きオーバークロックによる最適化

制限付きオーバークロックによる最適化とその動作

- 遅延の均衡化

すべてのデータ パスに一致する遅延を挿入します。

- Use Delay Absorption While Modeling with Latency

Model with latency to absorb design delays and prevent a timing mismatch between the original and generated model.

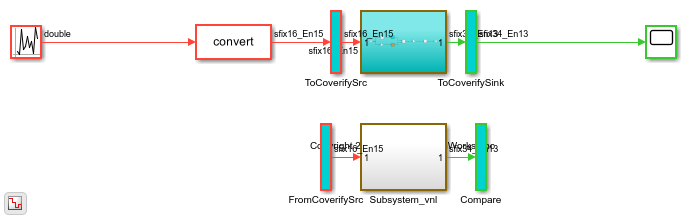

- 生成されたモデルと検証モデル

生成されたモデルとは、HDL コード生成で作成されるモデルのことで、HDL の実装アーキテクチャを示しレイテンシを含むモデルです。

- 生成された HDL コードの冗長なロジックと未使用ブロックの削除

生成された HDL コードの可読性を向上し、面積の利用効率性を最適化します。

- Simulink モデルの HDL コードでの未接続の端子の最適化

冗長なロジックの削除と共に、未使用の端子を生成された HDL コードで最適化。

- HDL Coder での定数演算の簡略化と設計の複雑度の低減

定数を簡略化し、数学演算を最適化する面積およびタイミングの最適化。

- イネーブルベースのマルチサイクル パス制約を使用してタイミング要件を満たす

合成ツール用のイネーブルベースの制約を生成して単一クロック モードのマルチサイクル パスのタイミング要件を満たす。

トラブルシューティング

HDL コード生成後の数値の不一致を解決する方法を説明します。