JFET アンプと周波数応答解析

この例では、N チャネル JFET に基づくオーディオ アンプ回路を示します。目標操作点は Vds = 5 V、Id = 2 mA、Vgs = -2 V とします。メーカーのデータシートでは、順伝達コンダクタンスと出力コンダクタンスの値をそれぞれ 3 mS、50 uS としています。これらの値を使用して、N-Channel JFET ブロックのマスクが入力されます。

バイアス抵抗の値は次のように計算されます。

抵抗 R1 は、実質的にゲートを接地につないでいます。そのため、抵抗 R3 の電圧は -Vgs で、2 V でなければなりません。したがって、R3 = -Vgs / Id = 2 / 2e-3 = 1 KΩ になります。

R3、JFET のドレイン-ソース接続、および R2 にかかる合計電圧は 15 V でなければなりません。したがって、R2 にかかる電圧は Vds = 5 V の場合に 8 V となり、R2 = 8 / 2e-3 = 4 KΩ になります。

C3 は、対象となる最も低い周波数 (20 Hz) では実質的に短絡となるくらい大きな値でなければなりません。C4 は、中帯域ゲインと比較したゲインの損失が約 6 dB になるように選択します。

Simulink® Control Design™ をお持ちの場合は、周波数応答をプロットするために、モデル JFETFrequencyResponse を開きます。[アプリ] タブの [制御システム] で、[モデル線形化器] をクリックします。モデル線形化器の [線形解析] タブの [線形化] セクションで、[ボード線図] をクリックします。Simulink ラインを右クリックし、[線形化のポイント] を選択することで、このモデルの線形化のポイントを定義します。

モデル

Simscape ログからのシミュレーション結果

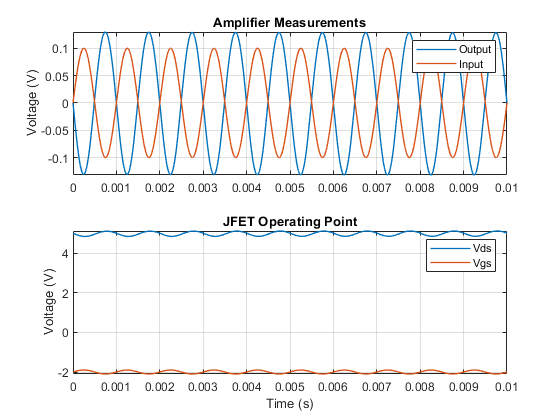

以下のプロットは、アンプ回路の電圧を示しています。上のプロットはアンプのゲインを示し、下のプロットは、JFET が目的の操作点付近でテストされていることを示します。

周波数応答

リアルタイム シミュレーションの結果

この例は、以下のプラットフォームでテストされました。

Intel® 3.5 GHz i7 マルチコア CPU と 4 GB の RAM を搭載した Speedgoat™ Performance リアルタイム ターゲット マシン。

3.5 GHz の Intel® Core XEON E3-1275v3 と 4 GB の RAM を搭載した dSPACE® SCALEXIO LabBox。

Simscape のローカル ソルバーを使用することで、このモデルを 50 マイクロ秒のステップ サイズでリアルタイム実行できます。サンプル レートが小さい場合、コールド キャッシュが原因で、最初のタスク実行中にタスク オーバーランが発生する可能性があります。このオーバーランを回避するには、選択したプラットフォームがこれらのオプションをサポートしている場合、タスク オーバーランの数を制限するか、リアルタイム アプリケーションの起動フェーズにおいてタスクのオーバーラン許容回数を制限するか、周期タスクのサンプル時間を延長することで、起動時の動作を緩和できます。