DDR4 Implementation Kit for JEDEC Raw Card B

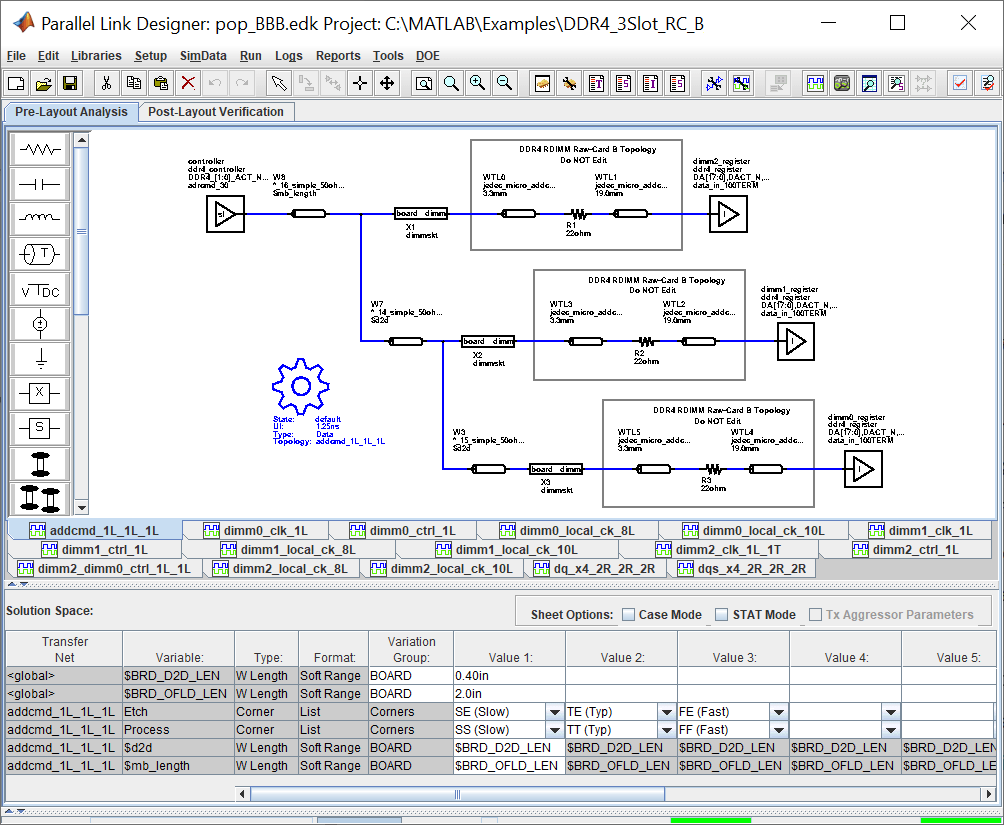

Implement a 3-slot DDR4 Raw Card B RDIMM interface for pre-layout analysis or post-layout verification.

This DDR4 Raw Card B RDIMM implementation signal integrity kit includes block diagrams, system configurations, transfer nets and libraries, which can be easily modified to match your exact implementation. You can modify the kit to match your exact DDR4 implementation. Then, perform complete pre-layout solution space analysis and/or full post-layout verification for waveform quality and timing margins.

Open DDR4 Raw Card B Kit

Open the DDR4 Raw Card B kit in the Parallel Link Designer app using the openSignalIntegrityKit function.

openSignalIntegrityKit("DDR4_3Slot_RC_B");

Kit Overview

Project name: DDR4_3Slot_RC_B

pop_BBB interface: A 3-slot DDR4 interface with all 3 slots populated with RDIMM modules

pop_XBB interface: A 3-slot DDR4 interface with 2 slots populated with RDIMM modules

pop_XXB interface: A 3-slot DDR4 interface with 1 slot populated with RDIMM modules

There are two independent DDR4 channels in the generic controller: DDR4_0 and DDR4_1. Only one channel represented in pre-layout analysis. Post-layout analysis automatically extracts and simulates all channels. This is a 288-pin buffered DDR4 RDIMM. There are 72-bits per channel (64 data, 8 ECC) and 3 RDIMM slots per channel: dimm0, dimm1 and dimm2. Each slot can be populated with Raw Card B DDR4 Registered DIMM modules.

This kit supports both HSPICE and IsSpice4 simulators. No specific version of either simulator is required when running this kit.

For more information about the 3-slot DDR4 Raw Card B implementation signal integrity kit, including block diagrams, system configurations, transfer nets and libraries, refer to the document DDR4_3slot_rcB.pdf that is attached to this example as a supporting file.