PCIe インターフェイスへのバス データ型のマッピング

DUT インターフェイス端子でバス データ型を使用する場合、インターフェイス端子を PCIe インターフェイスに直接マッピングできます。

バス データ型をマッピングすると、HDL Coder™ は一意のアドレスを PCIe インターフェイスにマッピングする各データ端子に割り当てます。最上位レベルと下位レベルのバスにレジスタ オフセット アドレスはありません。スカラーまたはベクトルの個々のバス要素のアドレス マッピングに連続性はありません。

バス要素のモデル化

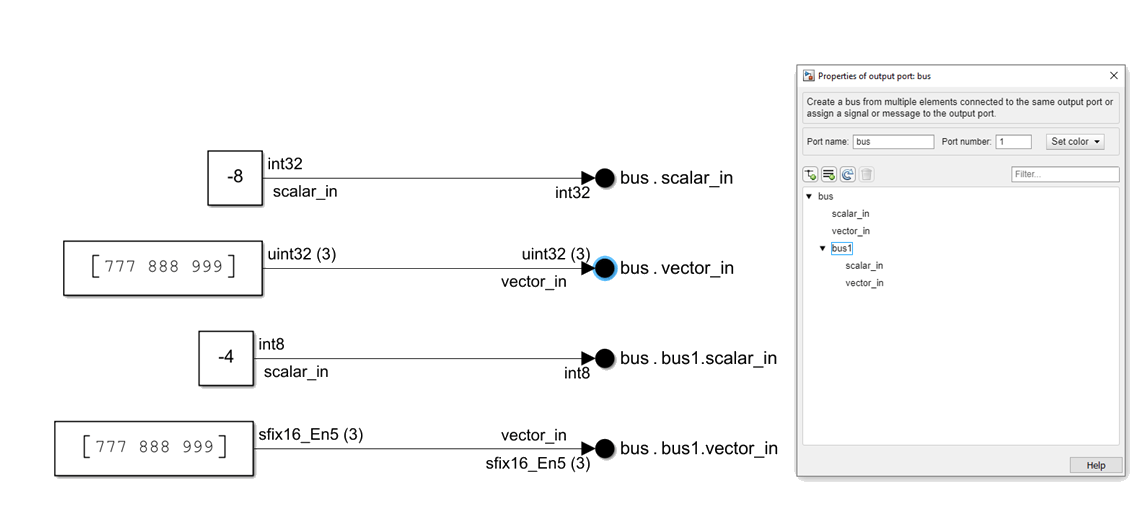

バス要素をモデル化するには、Bus Creator ブロックを使用するか、Bus Element ブロックを使用してバス端子を作成します。

Bus Creator ブロックを使用してバス要素をモデル化します。

Bus Element ブロックを使用してバス要素をモデル化します。

バス データ型を PCIe インターフェイスにマッピングする例については、Speedgoat Simulink プログラム可能 I/O モジュールでの FPGA プログラミングと構成を参照してください。