このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

ソフトウェアインザループ コード カバレッジ

この例では、ソフトウェアインザループ (SIL) モードを使用してモデル参照からコード カバレッジ メトリクスを収集する方法を説明します。

コード カバレッジ結果の生成

モデル slvnvdemo_counter_harness は Signal Editor ブロックを使用して slvnvdemo_counter モデルへのモデル参照に対する入力を指定するハーネス モデルです。

モデルはカバレッジ用に構成されますが、シミュレーション モードは Normal に設定されます。ノーマル シミュレーション モードでは、モデル カバレッジ データのみを収集できます。ソフトウェアインザループ カバレッジを収集するには、次のいずれかの方法を使用します。

モデル参照から、Model ブロックのブロック パラメーターで参照モデルのシミュレーション モードを設定します。Model ブロック

slvnvdemo_counterをクリックし、[Model ブロック] タブをクリックします。[シミュレーション モード] をSoftware-in-the-Loop (SIL)に設定します。ブロック アイコンの角が黒に変わり、ブロックのモデル名の下に (SIL) と表示されます。

[アプリ] タブで、[カバレッジ アナライザー] をクリックします。次に、[カバレッジ] タブで、[カバレッジの解析] をクリックします。Simulink Coverage® は SIL シミュレーション モードを使用する参照サブシステムの生成コードに対するカバレッジを収集します。

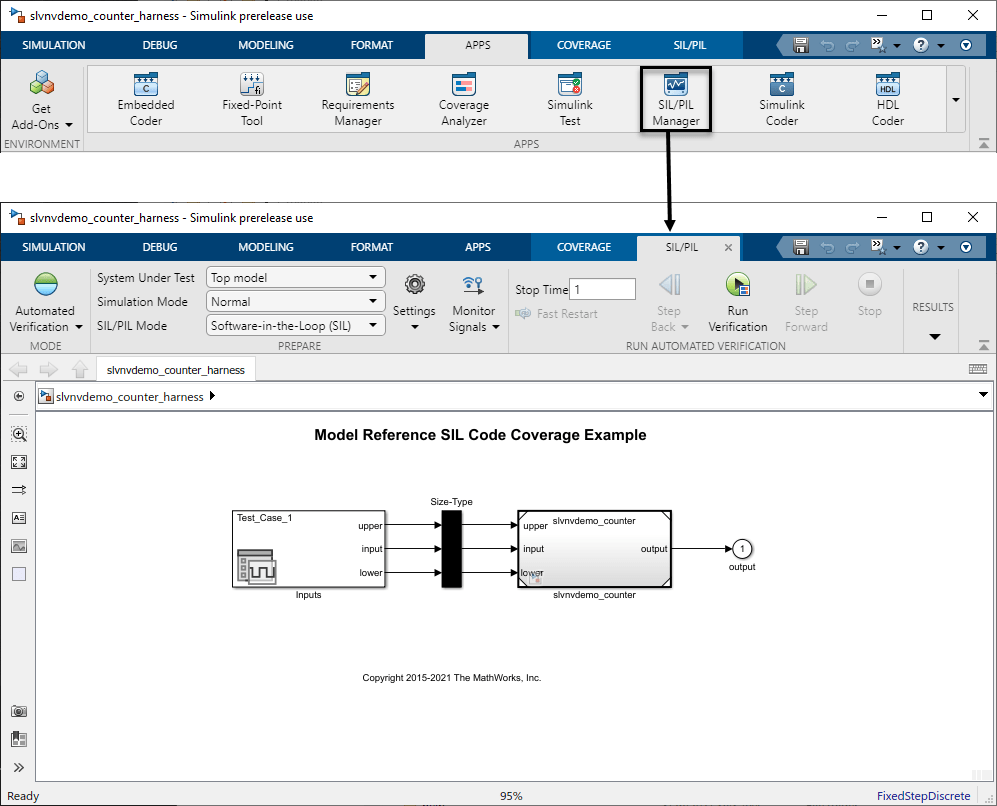

SIL/PIL マネージャー アプリを使用してシミュレーションを実行します。この方法は、最上位モデルと参照モデルのカバレッジを収集する場合、または [カバレッジ解析のスコープ] が

Entire Systemに設定されている場合に使用します。[アプリ] タブで、[SIL/PIL マネージャー] をクリックします。[検証の実行] をクリックします。Simulink Coverage® は SIL/PIL シミュレーションの生成コードのカバレッジを収集します。最上位モデルのカバレッジを収集する場合、[カバレッジの解析] ボタンは常にノーマル モード シミュレーションを実行し、コード カバレッジの結果を生成しないことに注意してください。

カバレッジに対するモデルの構成の詳細については、カバレッジ オプションの指定を参照してください。

カバレッジの詳細でカバレッジ結果を表示する

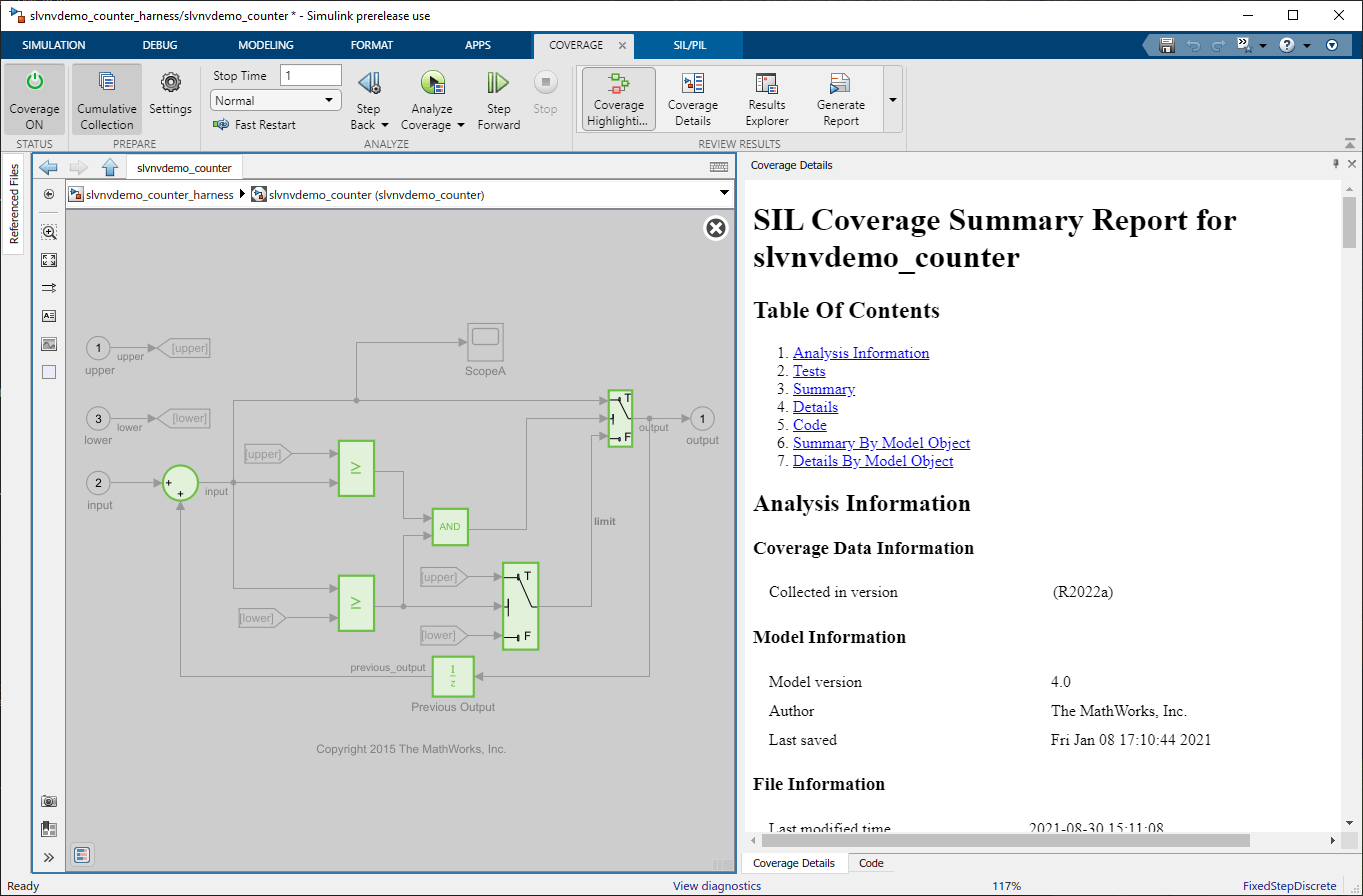

シミュレーションが完了すると、Simulink® で [コード] ペインと [カバレッジの詳細] ペインが開きます。一度に表示できるペインは 1 つだけです。[コード] ペインは既定の設定で開き、モデルから生成されたコードの詳細が含まれます。[コード] ペインの下部で、[カバレッジの詳細] タブをクリックします。

ペインにはメッセージ Coverage was not recorded for slvnvdemo_counter_harness が表示されます。このメッセージは、モデルが最上位モデル slvnvdemo_counter_harness ではなく、モデル参照 slvnvdemo_counter のカバレッジを収集するように構成されているために表示されます。モデル ブロック slvnvdemo_counter をダブル クリックして、このモデル参照のカバレッジ結果を表示します。

[カバレッジの詳細] ペインの最上部までスクロールして、これが SIL モード カバレッジの概要であることを確認します。

[詳細] をクリックして、カバレッジ レポートの [詳細] 節を表示します。この節には、ソース ファイル、これらのファイルで呼び出される関数、その関数を構成する個別のカバレッジ オブジェクティブの結果別に整理されたコード カバレッジがリストされます。

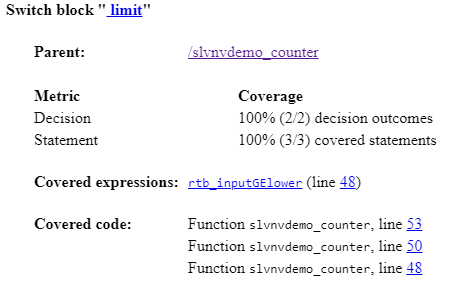

モデルで、limit と呼ばれる Switch ブロックをクリックして、各モデル オブジェクトの式と関数をリストするレポートの [モデル オブジェクト別の詳細] 節を確認します。たとえば、Switch ブロック limit は関数 slvnvdemo_counter.c の 48 行、50 行、53 行で判定カバレッジおよびステートメント コード カバレッジの対象となり、カバーされた式は rtb_inputGElower です。

コード ビューでカバレッジ結果を表示する

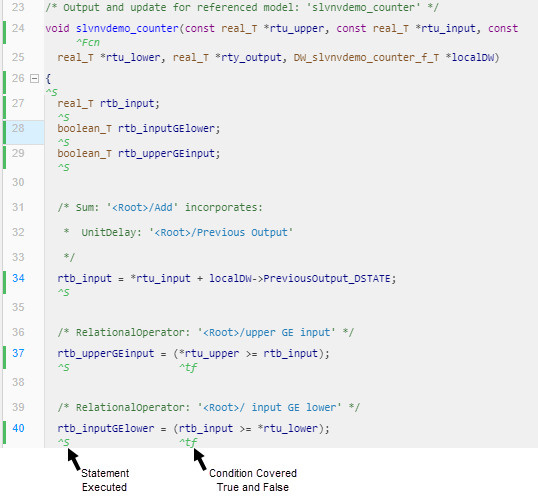

Embedded Coder® で作成されたコード ビューでカバレッジの結果も確認できます。[カバレッジの詳細] ペインの下部で、[コード] をクリックします。

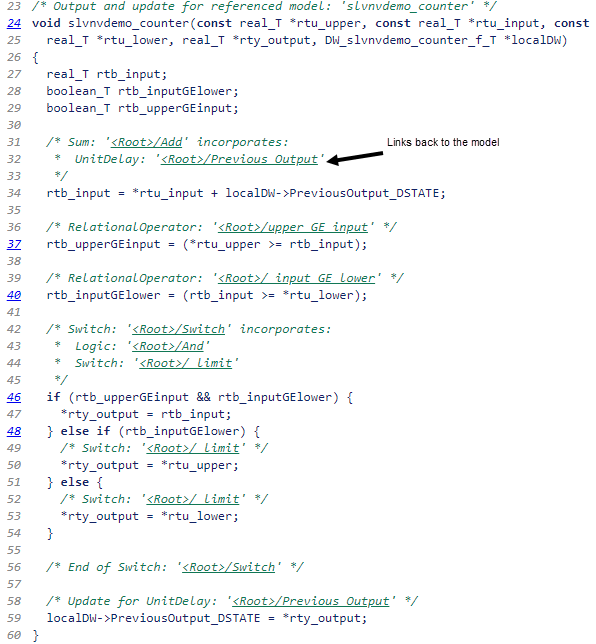

コードの各行には、フル カバレッジがあるかどうかを示す注釈があります。たとえば、40 行には次の注釈があります。

ステートメント

rtb_inputGElowerの下にある緑色の^Sは、この行が実行され、フル ステートメント カバレッジの対象となることを示しています。条件

rtb_input >= *rtu_lowerの下にある緑色の^tfは、条件の真と偽の両方のケースが実行され、条件は条件フル カバレッジをもつことを示しています。

コード ビューの注釈の詳細については、Code Coverage for Models in Software-in-the-Loop (SIL) Mode and Processor-in-the-Loop (PIL) Mode (Embedded Coder)を参照してください。

スタンドアロン カバレッジ レポートの作成と表示

スタンドアロン コード カバレッジ レポートを作成するには、[カバレッジ] タブで [レポートの生成] をクリックします。コード カバレッジ レポートには生成コードを表示する節が含まれます。

各コード ステートメントとロジック ブロックには、コードが生成されたソース ブロックを説明するコメントまたは一連のコメントが含まれます。各コメントには、モデルに戻り、モデルからコードへのマッピングに役立つリンクも含まれます。