このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

Simulinkを使用したレイズド コサイン フィルター設計の検証

Simulinkとコシミュレーション ウィザードのチュートリアルの概要

このチュートリアルでは、 HDL Verifier™を使用するSimulink® アプリケーションと、 Simulinkモデルをテストベンチとして使用します。このチュートリアルでは、 Simulinkと HDL シミュレーターをコシミュレーションする手順を実行して、 Verilog®で記述された単純なレイズド コサイン フィルターを検証します。

メモ

このチュートリアルには、 Simulink、 HDL Verifier、 Fixed-Point Designer™、およびModelSim®またはXcelium™が必要です$ HDL シミュレーター。このチュートリアルは、 HDL コシミュレーション ブロックの HDL コードのインポートを読んでいることを前提としています。

このチュートリアルでは、次の手順を実行します。

チュートリアル:チュートリアル ファイルのセットアップ (Simulink)

他の人がチュートリアル ファイルのコピーにアクセスできるようにするには、次の手順に従って自分のチュートリアル作業用のフォルダーを設定します。

MATLAB®インストール フォルダーの範囲外に、チュートリアル ファイルをコピーできるフォルダーを作成します。フォルダーは書き込み可能である必要があります。このチュートリアルでは、

MyTestsという名前のフォルダーを作成することを前提としています。次のディレクトリにあるすべてのファイルを、作成したフォルダーにコピーします。

matlabroot\toolbox\edalink\foundation\hdllink\demo_src\tutorial

ここで、

matlabrootは、システム上のMATLABルート ディレクトリです。これで、次のすべてのファイルが作業ディレクトリに存在しましたが、このチュートリアルでは、そのうちの 2 つだけが必要になります。

filter_tb.v(このチュートリアルでは使用されません)mycallback_solution.m(このチュートリアルでは使用されません)rcosflt_beh.v(このチュートリアルでは使用されません)rcosflt_rtl.vrcosflt_rtl.vhdrcosflt_tb.mdl

チュートリアル:コシミュレーションウィザードの起動 (Simulink)

MATLAB を起動します。

チュートリアル:チュートリアル ファイルのセットアップ (Simulink)で作成したディレクトリをMATLABの現在のディレクトリとして設定します。

MATLABコマンド プロンプトで、次のように入力します。

>>cosimWizard

このコマンドにより、コシミュレーション ウィザードが起動します。

チュートリアル:コシミュレーション ウィザードを使用した HDL コシミュレーション ブロックの構成

このチュートリアルでは、 HDL Cosimulationブロックの作成を支援するように設計された次のウィザード ページを順に進めていきます。

チュートリアル:コシミュレーション タイプの指定 (Simulink)

[コシミュレーション タイプ] ページで、次の手順を実行します。

HDL cosimulation withオプションを

Simulinkに設定したままにします。ModelSimを使用している場合は、 HDL Simulatorオプションを

ModelSimのままにしておきます。XceliumまたはVivado®を使用している場合は、 HDL Simulatorオプションを

Xceliumまたはに変更します。それぞれ$Vivado Simulator。HDL シミュレーターの実行可能ファイルがシステム パスに表示される場合は、デフォルト オプションのUse HDL simulator executables on the system pathオプションをそのままにしておきます。

これらの実行可能ファイルがパス上にない場合は、 協調シミュレーション タイプ— Simulinkブロックの説明に従って HDL シミュレーターのパスを指定します。

「Next」をクリックして、「HDL ファイル」ページに進みます。

チュートリアル:HDL ファイルを選択 (Simulink)

[HDL ファイル] ページで、次の手順を実行します。

HDL ファイルをファイル リストに追加します。

「Add」をクリックし、 チュートリアル:チュートリアル ファイルのセットアップ (Simulink)で作成したディレクトリを参照します。

Verilogの場合は、

rcosflt_rtl.vを選択します。VHDL®の場合は、rcosflt_rtl.vhdを選択します。予想どおりに識別されたファイル タイプを使用して、ファイル リスト内のファイルを確認します。

「Next」をクリックして、「HDL コンパイル」ページに進みます。

チュートリアル:HDL コンパイル コマンドの指定 (Simulink)

コシミュレーション ウィザードの [コンパイル コマンド] ウィンドウにデフォルトのコマンドがリストされます。このチュートリアルでは、これらのコマンドを変更する必要はありません。

独自のコードでコシミュレーション ウィザードを実行する場合、このウィンドウでコンパイル コマンドを追加または変更できます。たとえば、 -vlog01compatスイッチを追加できます。

ModelSimユーザー:[HDL Compilation] ペインは、次の図のようになります。

Xceliumユーザー:HDL コンパイル ペインは次の図のようになります。

「Next」をクリックして、「HDL モジュール」ペインに進みます。

MATLABコンソールにはコンパイル ログが表示されます。コンパイル中にエラーが発生した場合、そのエラーはステータス領域に表示されます。次のステップに進む前に、エラーを取り除くために可能な限り設定を変更してください。

チュートリアル:協調シミュレーションのシミュレーション オプションを選択します (Simulink)

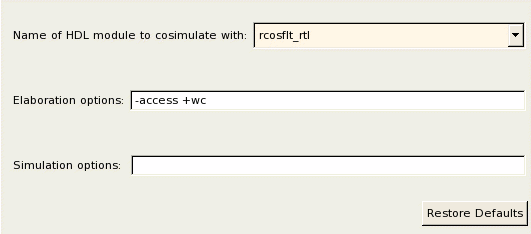

ModelSimまたはXceliumを使用している場合は、[シミュレーション オプション] ペインで次の手順を実行します。

協調シミュレーション用の HDL モジュール/エンティティの名前を指定します。

ドロップダウン リストから、

rcosflt_rtlを選択します。このモジュールは、コシミュレーションに使用するVerilog/ VHDLモジュールです。ドロップダウン リストに

rcosflt_rtlが表示されない場合は、ファイル名を手動で入力できます。ファイアウォール ポリシーで TCP/IP ソケット通信が許可されていない場合は、 Connection methodで

Shared Memoryを選択します。シミュレーション オプションは次の図のようになります。

Xceliumユーザー:HDL モジュールのオプションは次の図のようになります。

「Next」をクリックして、 「Simulinkポート」ペインに進みます。

コシミュレーション ウィザードは、指定された HDL モジュールとシミュレーション オプションを使用して、バックグラウンド コンソールで HDL シミュレーターを起動します。ウィザードが HDL シミュレータを起動した後、ウィザードはVerilog/ VHDLモデル

rcosflt_rtlの入力ポートと出力ポートを設定し、表示します。次のステップで。

Vivadoシミュレータを使用している場合、[シミュレーション オプション] ペインの外観は少し異なります。

Name of HDL module to cosimulate with は読み取り専用パラメーターで、 チュートリアル:HDL ファイルを選択 (Simulink)ステージで指定された最上位の HDL モジュールを表示します。

内部信号の波形ファイルを生成したい場合は、 Debug internal signalsパラメーターを

waveに設定します。このオプションはシミュレーションのパフォーマンスに影響を与える可能性があります。波形生成を無効にするには、このパラメーターをoffに設定します。HDL time precisionパラメーターを必要な時間精度に設定します。

「Next」をクリックして、 「Input/Output Ports」ペインに進みます。

コシミュレーション ウィザードは、指定された HDL モジュールとシミュレーション オプションを使用して、バックグラウンド コンソールで HDL シミュレーターを起動します。ウィザードが HDL シミュレータを起動した後、ウィザードはVerilog/ VHDLモデル

rcosflt_rtlの入力ポートと出力ポートを設定し、表示します。次のステップで。

チュートリアル:ポートタイプの指定

このステップでは、コシミュレーション ウィザードに、 rcosflt_rtlの入力ポートと出力ポートをそれぞれ含む 2 つのテーブルが表示されます。

コシミュレーション ウィザードは、各ポートのポート タイプを識別しようとします。ウィザードがポートを誤って識別した場合は、これらのテーブルを使用してポートの種類を変更できます。

入力ポートとして、

Clock、Reset、Input、またはUnusedから選択できます。 HDL Verifier は、コシミュレーション中にInputとマークされた入力ポートのみをSimulinkに接続します。HDL Verifier は、コシミュレーション中に

Outputとマークされた出力ポートをSimulinkに接続します。ウィザードとSimulink は、コシミュレーション中にUnusedとマークされた出力ポートを無視します。ClockおよびResetとして識別される信号のパラメーターは、後のステップで変更できます。

デフォルトのポートタイプを受け入れ、 「Next」をクリックして「Output Port Details」ページに進みます。

チュートリアル:出力ポートの詳細の指定

[出力ポートの詳細] ページで、次の手順を実行します。

バックプロパゲーション経由で継承するには、

filter_outのサンプル時間を -1 に設定します。Verilogコードから、コシミュレーション ウィザードが出力を S34,29 形式で表していることがわかります。次のフィールドを変更します。

データ型を

Fixedpointに設定Signedに署名します29までの小数部の長さ

.結果は次の画像のようになります。

Nextをクリックして、クロック/リセットの詳細ページに進みます。

チュートリアル:時計の設定と詳細のリセット

このチュートリアルでは、クロックPeriod (ns)を 20 に設定します。Verilogコードから、リセットが同期であり、アクティブな値が 1 であることがわかります。クロックの立ち上がりエッジによってトリガーされ、HDL デザイン全体を時間 1 ns でリセットできます。リセット信号には 15 ns の持続時間を使用します。

[クロック/リセットの詳細] ページで、次の手順を実行します。

クロック周期を 20 に設定します。

アクティブ エッジを

Risingのままにするか、設定します。リセットの初期値を 1 のままにするか、1 に設定します。

リセット信号の持続時間を 15 に設定します。

クロックとリセットは、次の図に示す同じ信号と同じになりました。

「Next」をクリックして、「開始時間の調整」ページに進みます。

チュートリアル:開始時間の調整を確認する

[Start Time Alignment] ページには、クロック信号とリセット信号の波形のプロットが表示されます。コシミュレーション ウィザードには、コシミュレーションを開始する HDL 時間が赤い線で表示されます。開始時間は、Simulink がHDL シミュレーターから最初の入力サンプルを取得する時間でもあります。

開始時間の調整を設定または確認する

クロックのアクティブ エッジは立ち上がりエッジです。したがって、HDL シミュレーターの時間 20 ns では、レイズド コサイン フィルターの登録された出力は安定しています。競合状態は存在せず、協調シミュレーションを開始するデフォルトの HDL 時間 (20 ns) がこのシミュレーションに必要なものです。開始時刻を変更する必要はありません。

「Next」をクリックしてブロック生成に進みます。

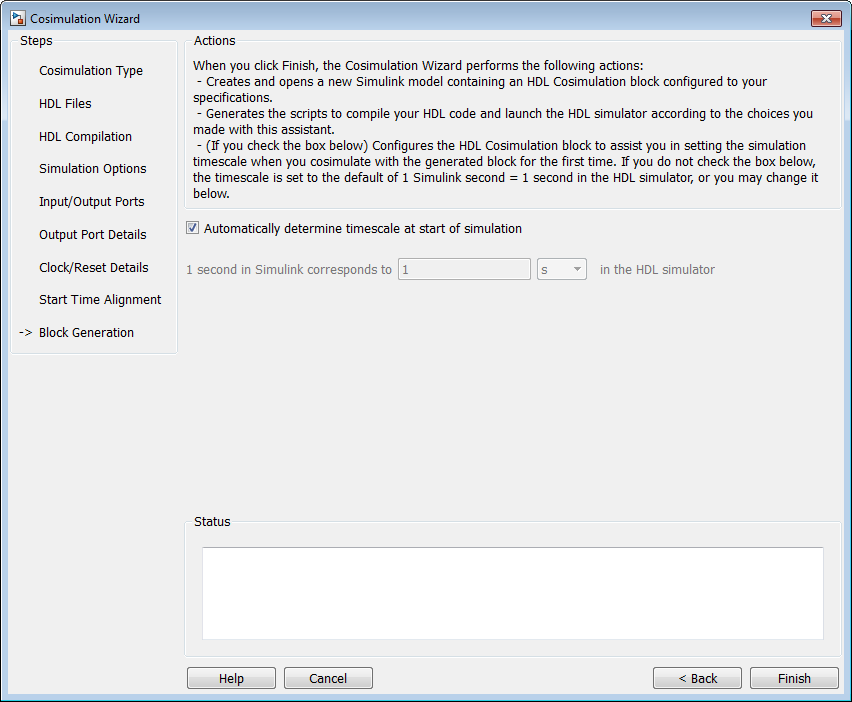

チュートリアル:ブロックの生成

HDL Cosimulationブロックを生成する前に、コシミュレーション ウィザードを終了する前にタイムスケールを決定するオプションがあります。あるいは、後でタイムスケールを計算するようにHDL Verifierに指示することもできます。検証ソフトウェアによるタイムスケール計算は、生成されたHDL Cosimulationブロックのすべての入出力ポートを接続し、シミュレーションを開始した後に行われます。

Automatically determine timescale at start of simulationを選択したままにしておきます (デフォルト)。後で、計算されたタイムスケールを表示し、シミュレーションを開始する前にその値を変更することができます。

[Finish]をクリックして、コシミュレーション ウィザード セッションを完了します。

チュートリアル:HDL 設計を検証するためのテストベンチを作成する

このチュートリアルでは、実際にテストベンチを作成しません。代わりに、完成したモデル (rcosflt_tb.mdl) は、 チュートリアル:チュートリアル ファイルのセットアップ (Simulink)で作成したディレクトリにあります。

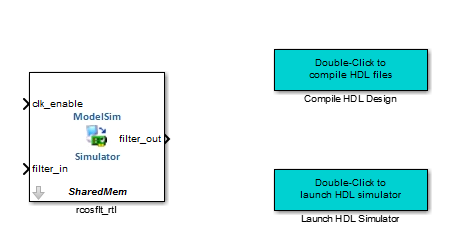

Finishをクリックすると、 Simulinkによってモデルが作成され、次の項目が設定されます。

HDL Cosimulationブロック

HDL デザインを再コンパイルするブロック (ブロックをダブルクリックすると起動されるスクリプトへのリンクが含まれます)

HDL シミュレーターを起動するブロック (ブロックをダブルクリックすると起動されるスクリプトへのリンクが含まれます)

しばらくモデルをそのままにして、次のステップに進みます。

Vivadoユーザー: Simulink はモデルを作成し、次の項目を設定します。

HDL Cosimulationブロック

共有ライブラリ(DLLファイル)を再生成するブロックです。ブロックには、ブロックをダブルクリックすると起動されるスクリプトへのリンクが含まれています。

rcosflt_tbチュートリアル:チュートリアル ファイルのセットアップ (Simulink)を開きます。このファイルには、 Simulinkテストベンチのモデルが含まれています。このテストベンチを使用して、対応するHDL Cosimulationブロックを生成した HDL デザインを検証します。

次のように、 HDL Cosimulationブロックをテストベンチ モデルに追加します。

新しく生成されたモデルからHDL Cosimulationブロックをこのテストベンチ モデルにコピーします。

constant ブロックと Convert ブロックがHDL Cosimulationブロックへの入力として整列し、バスが出力として整列するようにブロックを配置します。

テストベンチのブロックをHDL Cosimulationブロックに接続します。

スクリプト ブロックをテスト ベンチの下の領域にコピーします。モデルは次の図のようになります。

モデルを保存します。

チュートリアル:コシミュレーションの実行と HDL デザインの検証

Launch HDL Simulatorというラベルのブロックをダブルクリックして、HDL シミュレーターを起動します。

Vivadoユーザー: SimulinkツールストリップのSimulationタブで、 Runをクリックして協調シミュレーション。協調シミュレーションが開始されてから停止し、タイムスケールを決定するよう求められます。ステップ 3 に進みます。

HDL シミュレーターの準備ができたら、 Simulinkに戻り、シミュレーションを開始します。

タイムスケールを決定します。

コシミュレーション ウィザードの最後のページでAutomatically determine timescale at start of simulationオプションを選択したことを思い出してください。これを実行したため、 HDL Verifier はシミュレーションを開始する代わりにタイムスケール詳細 GUI を起動します。

HDL シミュレータとSimulink は両方とも、

filter_inポートとfilter_outポートを 1 秒でサンプリングします。ただし、HDL シミュレータでのサンプル時間はクロック周期 (2 ns) と同じである必要があります。Simulinkの

/rcosflt_rtl/clkサンプル時間を1(秒) に変更し、Enter を押します。次に、ウィザードはテーブルを更新します。次の図は、新しいタイムスケールを示しています。Simulinkの 1 秒は、HDL シミュレータの 2e-008 に対応します。

「OK」をクリックして「タイムスケールの詳細」を終了します。

シミュレーションを再開します。

テストベンチ モデルのスコープからの結果を検証します。このスコープには、レイズド コサイン フィルターへの入力の遅延バージョンとそのフィルターの出力の両方が表示されます。このフィルター出力の出力を直接サンプリングすると、シンボル間干渉は発生しません。

このステップで、 Simulinkチュートリアルで使用するコシミュレーション ウィザードは終了です。