Simscape モデルからの FPGA プラットフォーム用の HDL コードの生成

HDL Coder™ と Simscape™ があれば、FPGA プラットフォームに展開するための HDL コードをモデルから生成できます。アドバイザーは、Simscape モデルを HDL Coder が HDL コードの生成に使用する Simulink® 実装モデルに変換します。

Simscape モデルを HDL コードに変換すると、以下が可能になります。

Simscape の物理システム モデリング機能を利用する。

FPGA の再設定変更とパラレル化機能を使用して、モデルのプロトタイプを迅速に作成する。

ハードウェアインザループ (HIL) を使用して HDL 実装をリアルタイムでシミュレートする。

Simscape HDL ワークフロー アドバイザーを実行する前に、遅延および有効な実行時パラメーターを除外するようネットワークを構成してください。HDL Coder における Simscape モデルの機能および制限事項の詳細については、Simscape ハードウェアインザループ ワークフロー入門 (HDL Coder)を参照してください。

Simscape HDL ワークフロー アドバイザーを使用した HDL コードの生成

この例では、Simscape HDL ワークフロー アドバイザーを使用して Simscape モデルを HDL コードに変換する方法を示します。

HDL コード生成の準備が整った Simscape モデルを開くには、以下を入力します。

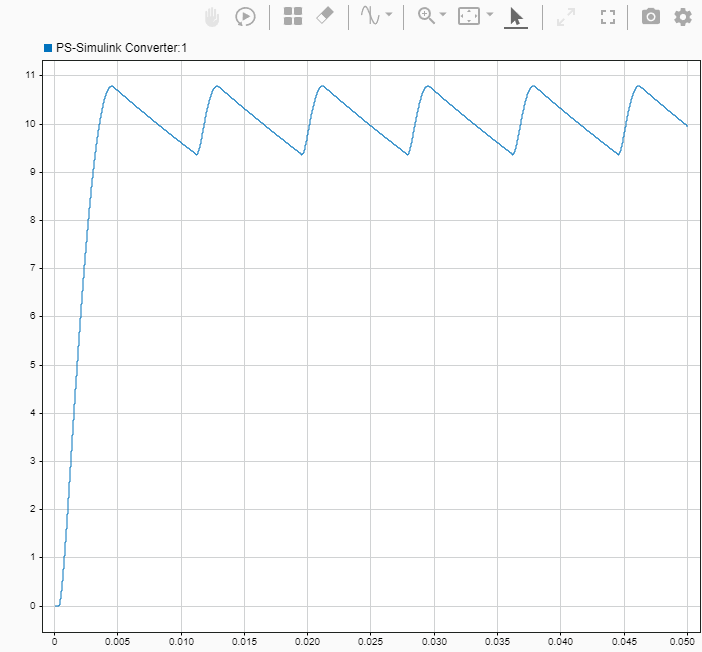

openExample('simscape_shared/FullWaveBridgeRectifierForSimscapeHDLAdvisorExample')比較用のベースライン結果を生成します。

baselineModel = "FullWaveBridgeRectifierForSimscapeHDLAdvisor"; sim(baselineModel) runIDs = Simulink.sdi.getAllRunIDs; runID = runIDs(end); run = Simulink.sdi.getRun(runID); signal1 = run.getSignalByIndex(1); signal1.checked = true; Simulink.sdi.view

ベースライン シミュレーションでは、全波ブリッジ整流器の負荷電圧について想定どおりの結果が返されます。

モデルの Simscape HDL ワークフロー アドバイザーを実行します。

sschdladvisor(baselineModel)

[すべて実行] をクリックして、アドバイザーですべてのステップを実行します。実装モデルが生成されるまで待ちます。アドバイザーは、HDL コード生成でモデルのロバスト性を向上させるヒントを提供します。

Simscape HDL ワークフロー アドバイザーが実装モデルを生成すると、アドバイザーはタスクがパスしたことをレポートし、生成された実装モデル

gmStateSpaceHDL_FullWaveBridgeRectifierForSへのリンクを表示します。そのリンクをクリックして、生成された実装モデルを開きます。

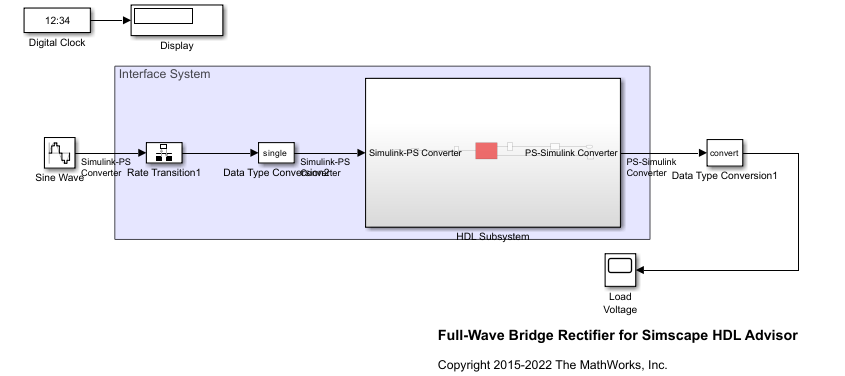

モデルには、元のモデルのブロックと、HDL ワークフロー アドバイザーをサポートする新しいブロックが含まれています。

Digital Clock、Display、Sine Wave、および Load Voltage — 元のモデルの機能を制御します。

Rate Transition1— 異なるレートで動作するブロック間でデータの転送を処理します。Data Type Conversion1、Data Type Conversion2— 倍精度と単精度のデータ型間で変換を行います。HDL コード生成には単精度データが必要です。HDL Subsystem— Simscape ネットワークの HDL コード生成互換バージョンが含まれています。Load Voltage Scope ブロック — 負荷電圧を表示します。

モデル名をワークスペース変数として保存します。

HDLmodelname = 'gmStateSpaceHDL_FullWaveBridgeRectifierForS';シミュレーションをベースライン結果と比較するために実装モデルを準備します。

自動生成されたモデルを確認し、残留ブロックを削除して、モデルをより良く整えます。このモデルでは、Digial Clock ブロックと Display ブロックは不要ですが、シミュレーションの結果の妨げとなることはありません。

Scope ブロックへの入力信号を右クリックし、[選択した信号のログ] をクリックします。

メモ

モデルの剛性が高すぎる場合、検証の不一致が発生する可能性があります。モデルの剛性のチェックについては、Simscape のスティッフネス影響分析を参照してください。

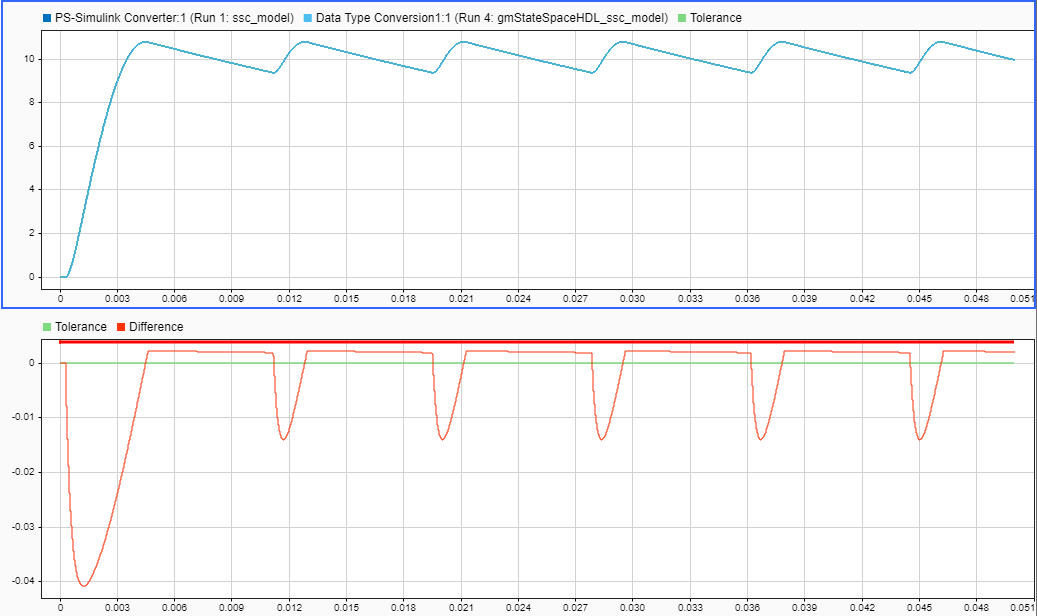

HDL サブシステムが元の Simscape モデルに対応していることを確認するため、モデルをシミュレートし、結果をベースライン シミュレーションの結果と比較します。

sim(HDLmodelname) runIDs = Simulink.sdi.getAllRunIDs; runID1 = runIDs(end - 1); % Baseline model runID2 = runIDs(end); % HDL implementation model run1 = Simulink.sdi.getRun(runID1); run2 = Simulink.sdi.getRun(runID2); sigID1 = getSignalIDByIndex(run1,1); sigID2 = getSignalIDByIndex(run2,1); compBaseline1 = Simulink.sdi.compareSignals(sigID1,sigID2); Simulink.sdi.view

結果はベースライン結果に類似しています。Simscape モデルは HDL コード生成と互換性があります。

実装から HDL コードを生成します。

HDL 実装モデルで、[コンフィギュレーション パラメーター] ウィンドウを開きます。[HDL コード生成] を展開して [レポート] を選択します。[トレーサビリティ レポートの生成] と [リソース利用レポートを生成] を選択します。

関数

hdlsetupを実行します。hdlsetup(HDLmodelname)

### AlgebraicLoopMsg value is set from 'warning' to 'error' (revert). ### BlockReduction value is set from 'on' to 'off' (revert). ### ConditionallyExecuteInputs value is set from 'on' to 'off' (revert). ### DefaultParameterBehavior value is set from 'Tunable' to 'Inlined' (revert). ### FixedStep value is set from 'Auto' to 'auto' (revert). ### InheritOutputTypeSmallerThanSingle value is set from 'off' to 'on' (revert). ### ProdHWDeviceType value is set from '32-bit Generic' to 'ASIC/FPGA->ASIC/FPGA' (revert). ### SingleTaskRateTransMsg value is set from 'none' to 'error' (revert). ### The listed configuration parameter values are modified as a part of hdlsetup. Please refer to hdlsetup document for best practices on model settings.

モデルとサブシステムのパラメーター設定を保存します。

hdlsaveparams(HDLmodelname)

%% Set Model 'gmStateSpaceHDL_FullWaveBridgeRectifierForS' HDL parameters hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'FPToleranceValue', 1.000000e-03); fpconfig = hdlcoder.createFloatingPointTargetConfig('NATIVEFLOATINGPOINT' ... , 'LatencyStrategy', 'Min' ... ); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'FloatingPointTargetConfiguration', fpconfig); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'HDLSubsystem', 'gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem'); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'MaskParameterAsGeneric', 'on'); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'Oversampling', 55); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'UseFloatingPoint', 'on'); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector', 'Architecture', 'MATLAB Datapath'); % Set SubSystem HDL parameters hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update/Multiply State', 'SharingFactor', 1);検証モデル生成の設定を保存します。

hdlset_param(HDLmodelname, 'GenerateValidationModel','on')

HDL コードを生成します。

makehdl('gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem')### Generating HDL for 'gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem'. ### Using the config set for model gmStateSpaceHDL_FullWaveBridgeRectifierForS for HDL code generation parameters. ### Running HDL checks on the model 'gmStateSpaceHDL_FullWaveBridgeRectifierForS'. ### Begin compilation of the model 'gmStateSpaceHDL_FullWaveBridgeRectifierForS'... ### Begin compilation of the model 'gmStateSpaceHDL_FullWaveBridgeRectifierForS'... ### Working on the model 'gmStateSpaceHDL_FullWaveBridgeRectifierForS'... ### The code generation and optimization options you have chosen have introduced additional pipeline delays. ### The delay balancing feature has automatically inserted matching delays for compensation. ### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays. ### Output port 1: 1 cycles. ### Working on... GenerateModel ### Begin model generation 'gm_gmStateSpaceHDL_FullWaveBridgeRectifierForS' .... ### Rendering DUT with optimization related changes (IO, Area, Pipelining)... ### Model generation complete. ### Generating new validation model: gm_gmStateSpaceHDL_FullWaveBridgeRectifierForS_vnl. ### Validation model generation complete. ### Begin VHDL Code Generation for 'gmStateSpaceHDL_FullWaveBridgeRectifierForS'. ### Unused logic removed during HDL code generation. To highlight the logic removed, click the following MATLAB script: highlightRemovedDeadBlocks.m ### To clear highlighting, click the following MATLAB script: clearHighlightingRemovedDeadBlocks.m ### MESSAGE: The design requires 55 times faster clock with respect to the base rate = 3.33333e-06. ### Begin VHDL Code Generation for 'HDL_Subsystem_tc'. ### Working on HDL_Subsystem_tc as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\HDL_Subsystem_tc.vhd. ### Code Generation for 'HDL_Subsystem_tc' completed. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector/nfp_mul_single as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\nfp_mul_single.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update/nfp_add_single as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\nfp_add_single.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Output/Multiply State/dot_product_2 as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\dot_product_2.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Output as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Output.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update/Bias as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Bias.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update/Multiply Input/dot_product_1 as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\dot_product_1.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update/Multiply State/dot_product_1 as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\dot_product_1_block.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\State_Update.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector/nfp_relop_single as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\nfp_relop_single.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector/nfp_uminus_single as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\nfp_uminus_single.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Generate_Mode_Vector.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Mode_Selection.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Iteration Manager/Counter Limited/Increment Real World as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Increment_Real_World.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Iteration Manager/Counter Limited/Wrap To Zero as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Wrap_To_Zero.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Iteration Manager/Counter Limited as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Counter_Limited.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Iteration Manager/Compare To Constant as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Compare_To_Constant.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Iteration Manager as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Mode_Iteration_Manager.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\HDL_Algorithm.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\HDL_Subsystem.vhd. ### Generating package file hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\HDL_Subsystem_pkg.vhd. ### Code Generation for 'gmStateSpaceHDL_FullWaveBridgeRectifierForS' completed. ### Creating HDL Code Generation Check Report HDL_Subsystem_report.html ### HDL check for 'gmStateSpaceHDL_FullWaveBridgeRectifierForS' complete with 0 errors, 3 warnings, and 3 messages. ### HDL code generation complete.

HDL コード生成レポートを開くには、

HDL_Subsystem_report.htmlのハイパーリンクをクリックします。HDL コード生成レポートには、生成されたエラーまたは警告が含まれます。レポートには、FPGA 展開のリソース要件を記述するリソース利用レポートへのリンクが含まれます。

アドバイザーは、生成された HDL コードと検証モデルを

hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForSディレクトリに保存します。生成されたコード ファイルの名前はHDL_Subsystem_tc.vhdです。

参考

関数

hdladvisor(HDL Coder) |hdlsaveparams(HDL Coder) |hdlset_param(HDL Coder) |hdlsetup(HDL Coder) |makehdl(HDL Coder) |simscape.findNonlinearBlocks|sschdladvisor(HDL Coder)