このページは前リリースの情報です。該当の英語のページはこのリリースで削除されています。

スタンドアロン FPGA ボード

Intel® ボードまたは Xilinx® ボードでの HDL コードの生成と展開

スタンドアロン Intel または Xilinx FPGA ボードで設計を展開するには、HDL Coder™ Support Package for Intel FPGA Boards または HDL Coder Support Package for Xilinx FPGA Boards をそれぞれインストールしなければなりません。インストールについては、HDL Coder でサポートされているハードウェアを参照してください。

クラス

hdlcoder.Board | SoC カスタム ボードを記述するボード登録オブジェクト |

hdlcoder.ReferenceDesign | SoC リファレンス設計を記述するリファレンス設計登録オブジェクト |

hdlcoder.WorkflowConfig | Configure HDL code generation and deployment workflows |

関数

トピック

IP コアの生成

- AXI4 スレーブ インターフェイスの生成のための設計のモデル化

スカラー端子、ベクトル端子、バス データ型の AXI4 または AXI4-Lite インターフェイス用のモデルの設計および値の読み戻し方法。 - AXI4-Stream インターフェイス生成向けのモデル設計

AXI4-Stream ベクトルまたはスカラー インターフェイス生成向けのモデルの設計法 - AXI4-Stream Video インターフェイス生成向けのモデル設計

AXI4-Stream Video インターフェイスをもつ IP コア生成のためのモデルの設計法。 - AXI4 Master インターフェイスを生成するためのモデル設計

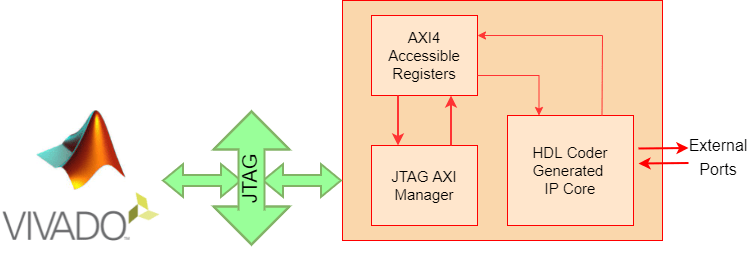

AXI4 Master プロトコルの説明および AXI4-Master インターフェイスを備えた IP コアの生成用にモデルを設計する方法の説明。 - スタンドアロン FPGA デバイス向けの IP コアの生成ワークフロー

スタンドアロン FPGA デバイスを使用した IP コアの生成ワークフローの使用方法および IP コアのリファレンス設計への組み込み方法を学習します。

Xilinx のプログラムと Intel ボード

- ターゲット FPGA ボードまたは SoC デバイスのプログラム

ターゲット Intel または Xilinx ハードウェアをプログラムする方法。

トラブルシューティング

IP コアの生成ワークフローと Simulink Real-Time FPGA I/O ワークフローでのタイミング エラーの解決

Vivado ベースのボードでの IP コアの生成ワークフローまたは Simulink Real-Time FPGA I/O ワークフローの [FPGA ビットストリームのビルド] ステップにおけるタイミング エラーを解決します。