ハードウェア ソフトウェア展開

ハードウェア ソフトウェア モデルのターゲット ハードウェアへの展開および実行

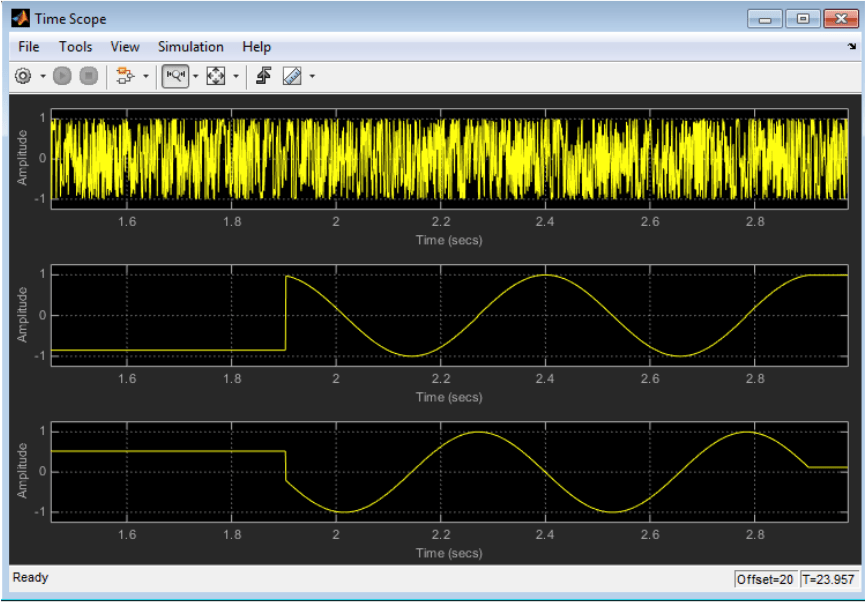

ソフトウェア インターフェイス モデルから C コード (Embedded Coder® が必要) を生成し、エクスターナル モードまたはプロセッサインザループ (PIL) モードを使用して、ハードウェア ソフトウェア モデルをターゲット ハードウェア上に展開し、実行します。入力は、次で構成される SoC デバイスの展開可能なモデルです。

HDL IP コアを含む元のモデルから生成されたビットストリーム。

プロセッサと FPGA 間の通信および組み込みプロセッサの C コード生成が可能となるように構成されたデバイス ドライバーを含むソフトウェア インターフェイス モデル。

出力は、ターゲット ハードウェアで実行されるハードウェア ソフトウェア デバイス用に生成されたコードです。

ワークフローの詳細については、FPGA および SoC ハードウェアをターゲットにする方法の概要を参照してください。

トピック

- Choose a Method to Interact with IP Cores on Target Hardware

Choose a software interface method to interact with IP cores running on target hardware.

- プロセッサと FPGA の同期

HDL ワークフロー アドバイザーでは、組み込みシステム統合プロジェクトで使用するカスタム IP コアを生成する場合にプロセッサと FPGA に対して [プロセッサ/FPGA 同期] モードを選択できます。