# Algorithm Development Using Model-Based Design

Eric Cigan

MathWorks

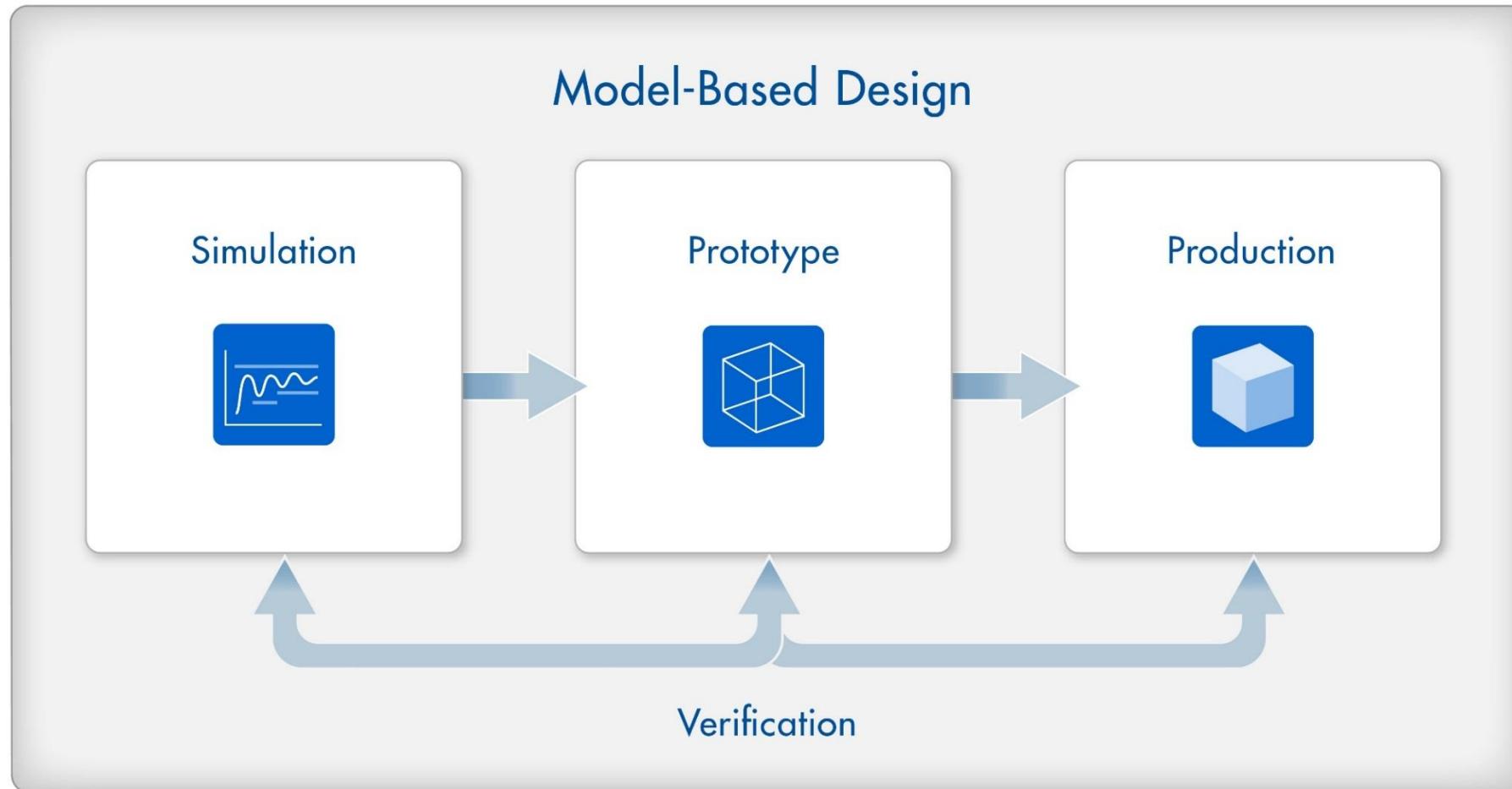

# Model-Based Design

A single shared development environment

# Model-Based Design

A single shared development environment

**Verify operation before committing to hardware**

**Validate performance on chip**

**Deploy design on target system**

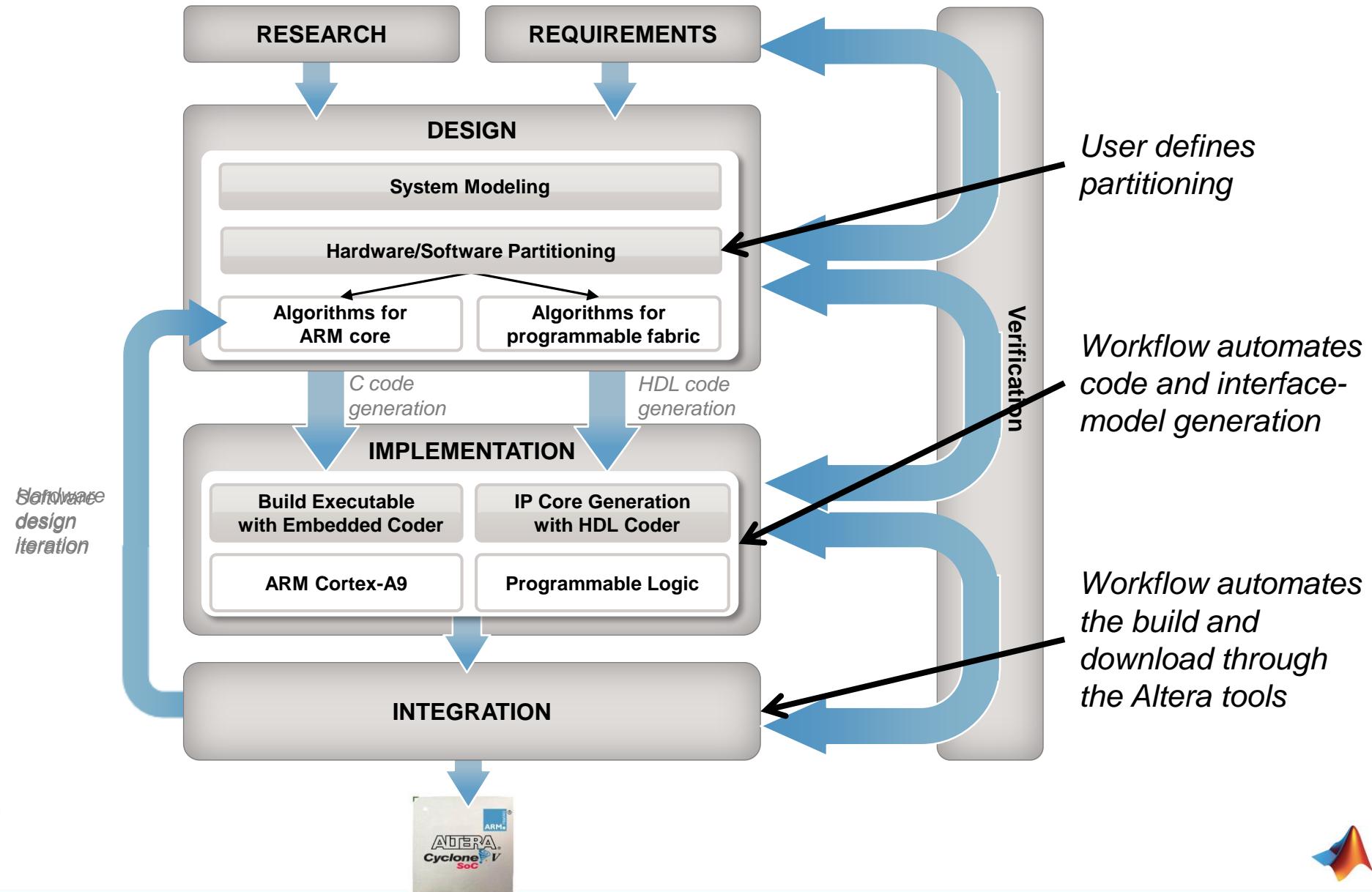

# Model-Based Design Workflow for Altera SoCs

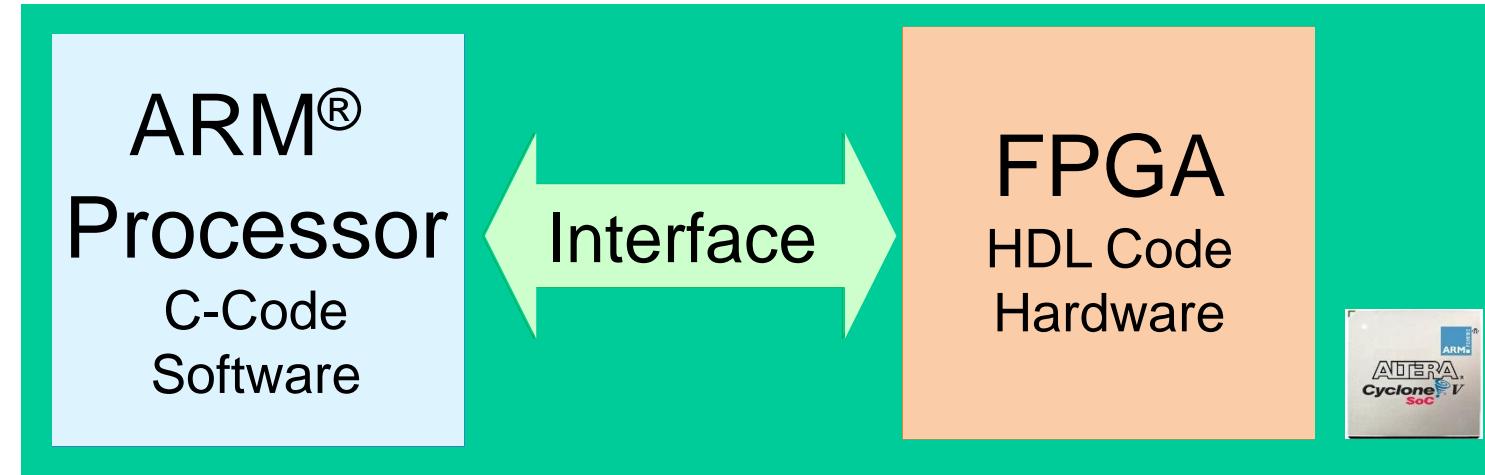

# SoC Design Challenge

# SoC Design Challenge

ARM®

Processor

C-Code

Software

- Typically programmed in C

- Often runs a Linux operating system

- Well-established workflows exist

## CHALLENGES

- FPGA Designers not familiar with programming processors

- What should run on the processor vs. the FPGA?

# SoC Design Challenge

FPGA

HDL Code

Hardware

- Typically programmed in VHDL/Verilog

- Established workflows exist

## CHALLENGES

- DSP/Processor programmers not familiar with FPGA Design

- What should run on the FPGA vs. the processor?

# SoC Design Challenge

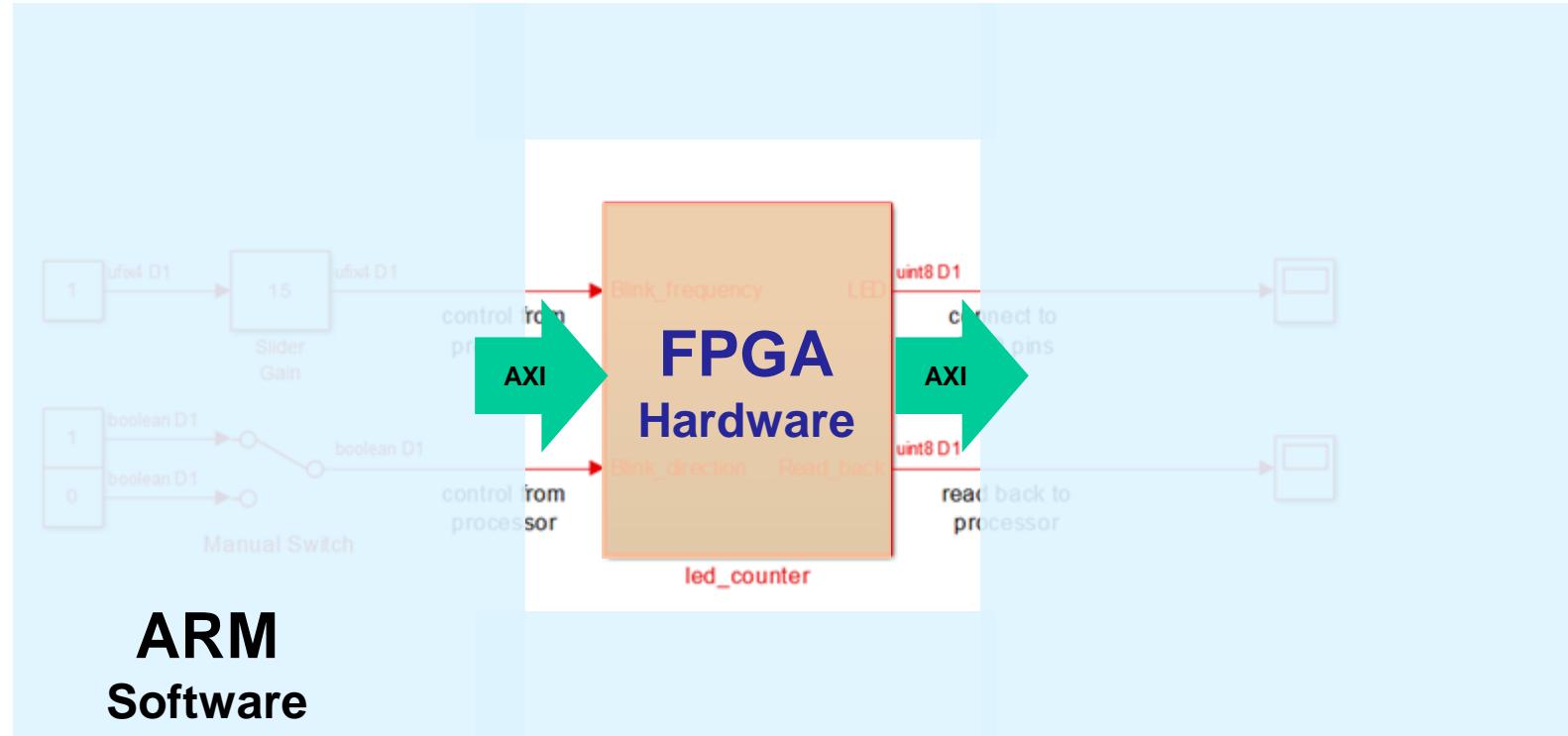

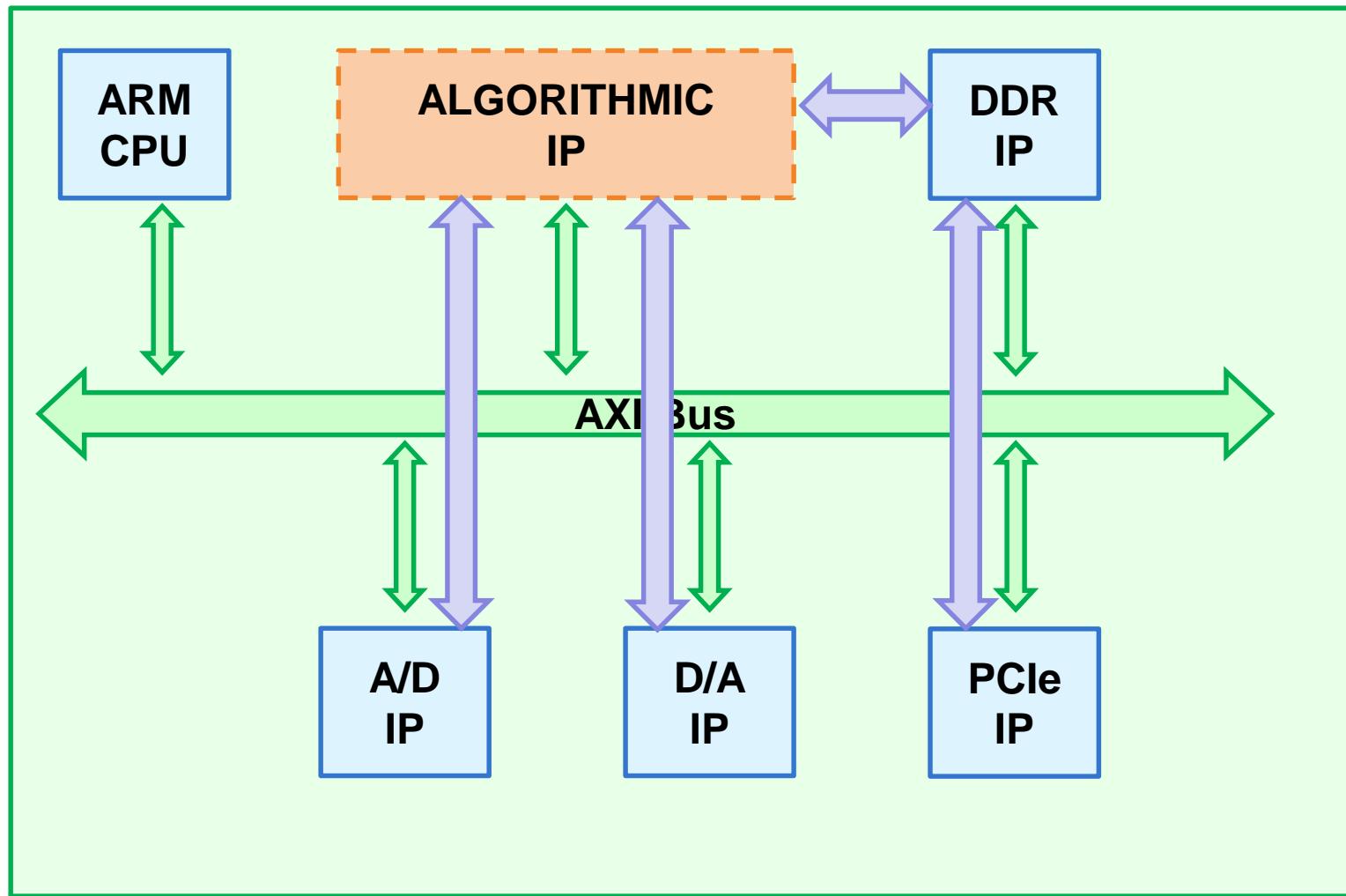

- Altera SoCs use “standard” AXI interface between FPGA and ARM

## CHALLENGES

- No established rules for hooking up the interface

- Many different “flavors” of AXI for different bandwidth requirements

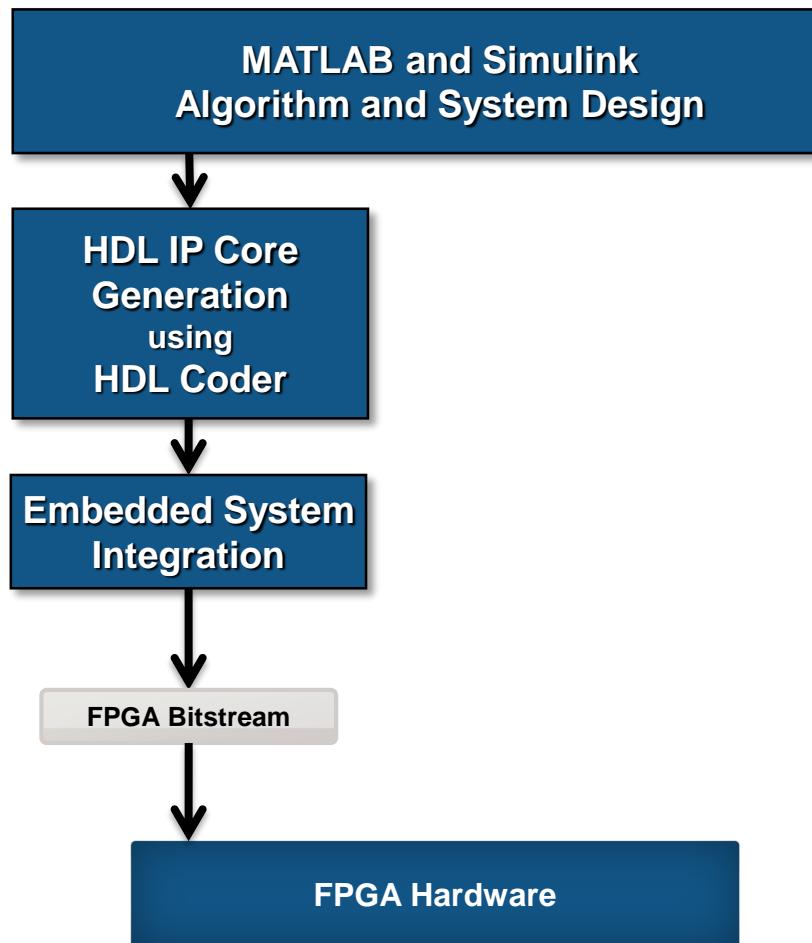

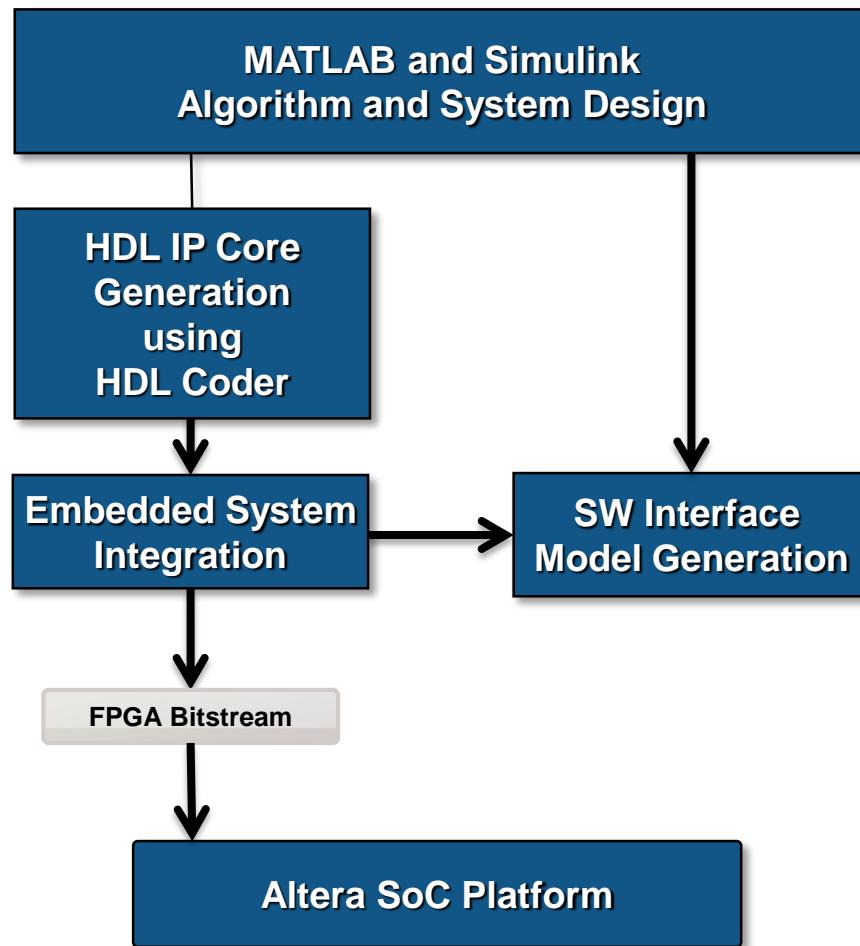

# SoC Model-Based Design Workflow

# SoC Model-Based Design Workflow

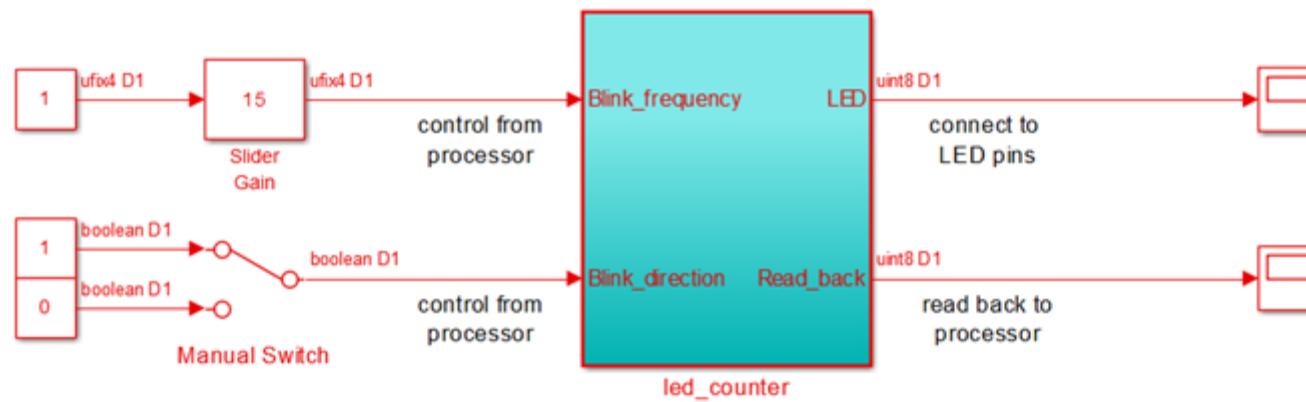

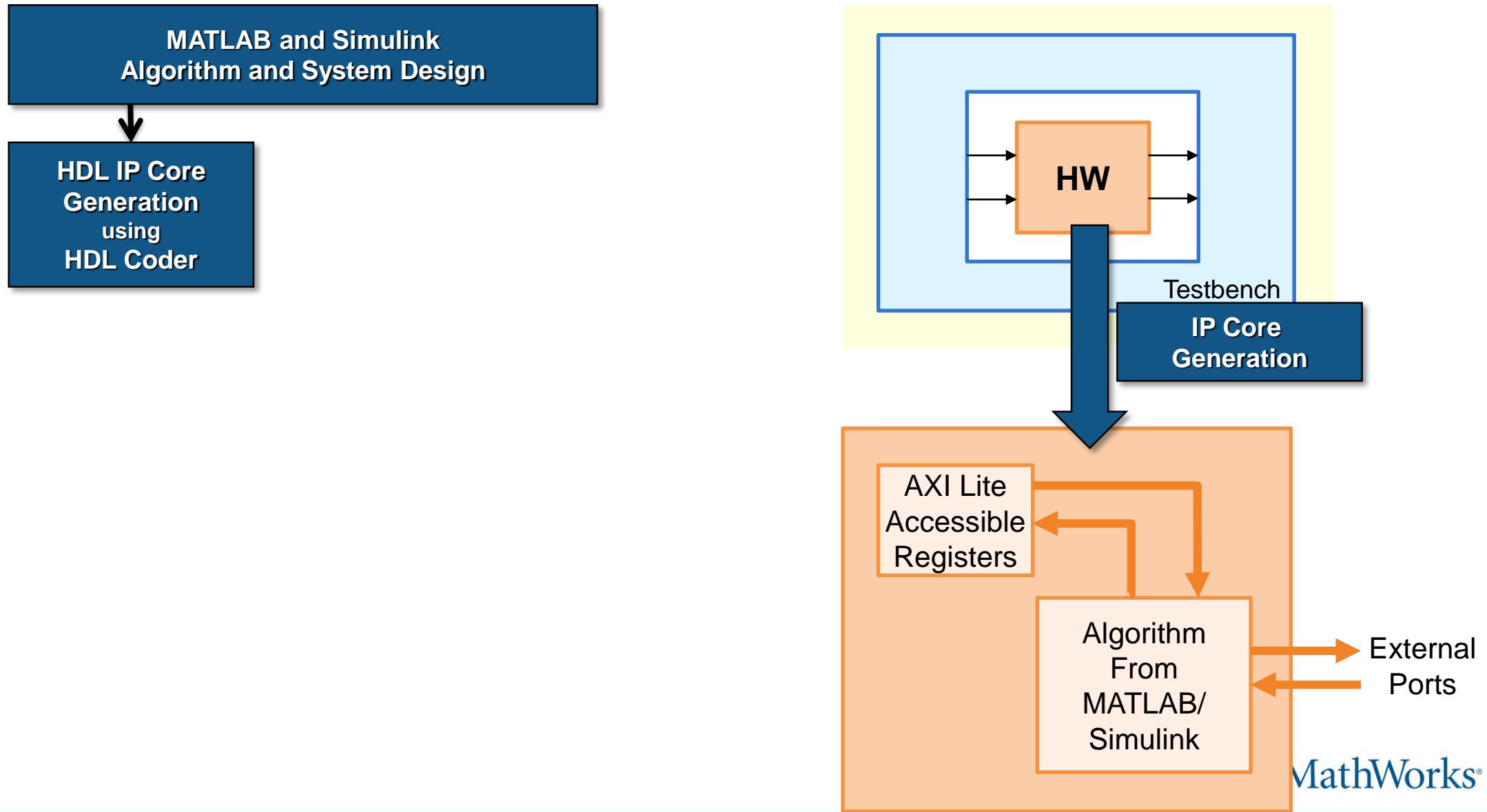

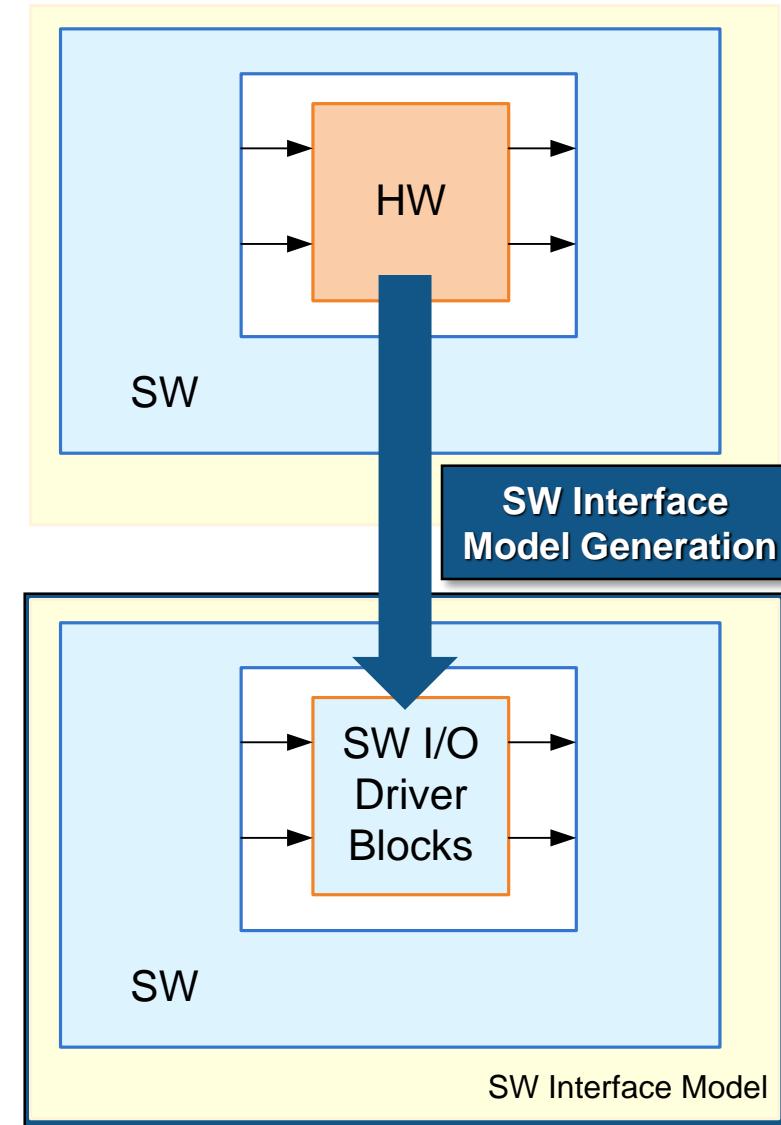

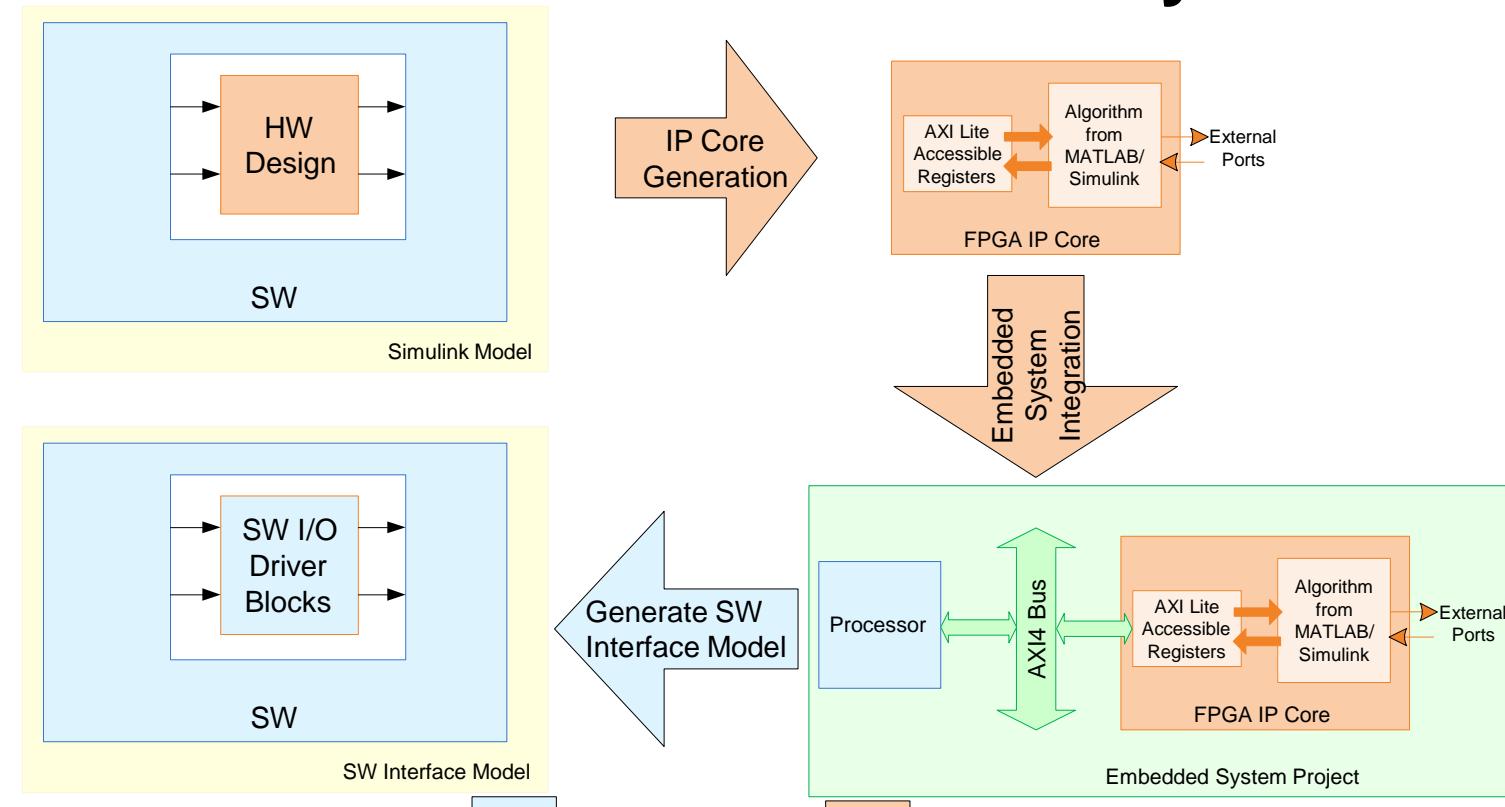

# IP Core Workflow

# IP Core Workflow

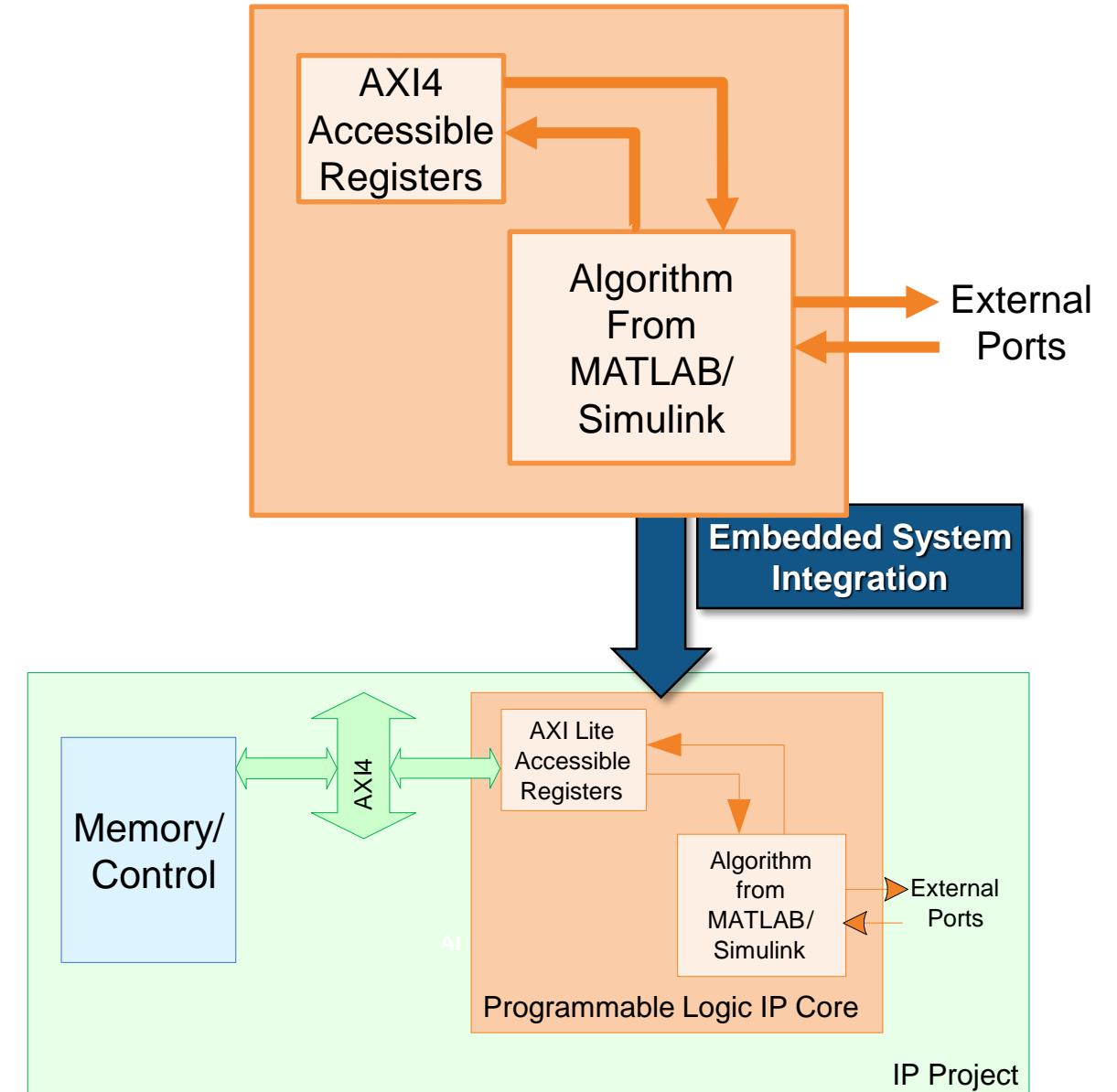

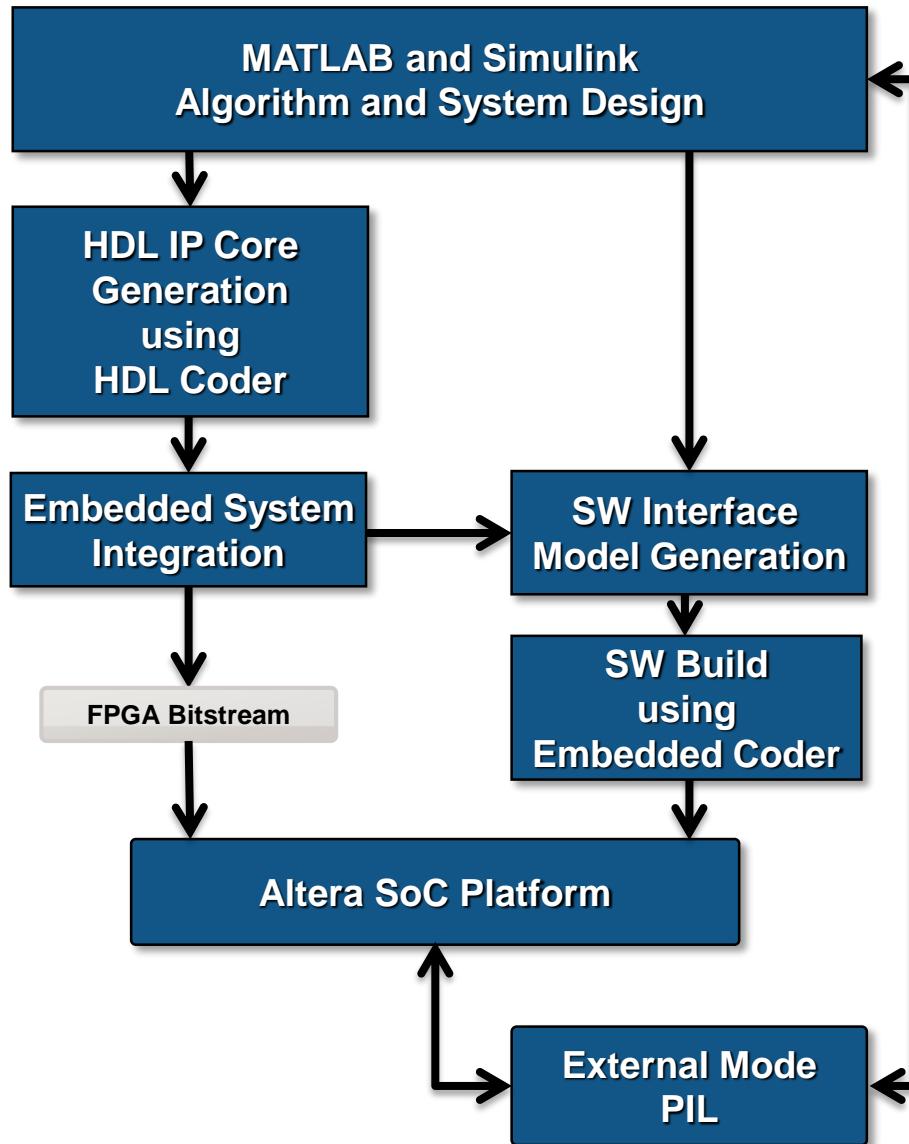

# SoC Model-Based Design Workflow

# SoC Model-Based Design Workflow

- Real-time Parameter Tuning and Verification

- External Mode

- Processor-in-the-loop

# SoC Hardware/Software Workflow Summary

# Target Platforms Supported with Model-Based Design for Altera SoCs

Altera Cyclone V SoC Development Kit

Arrow SoCKit

Custom Cyclone V SoC boards

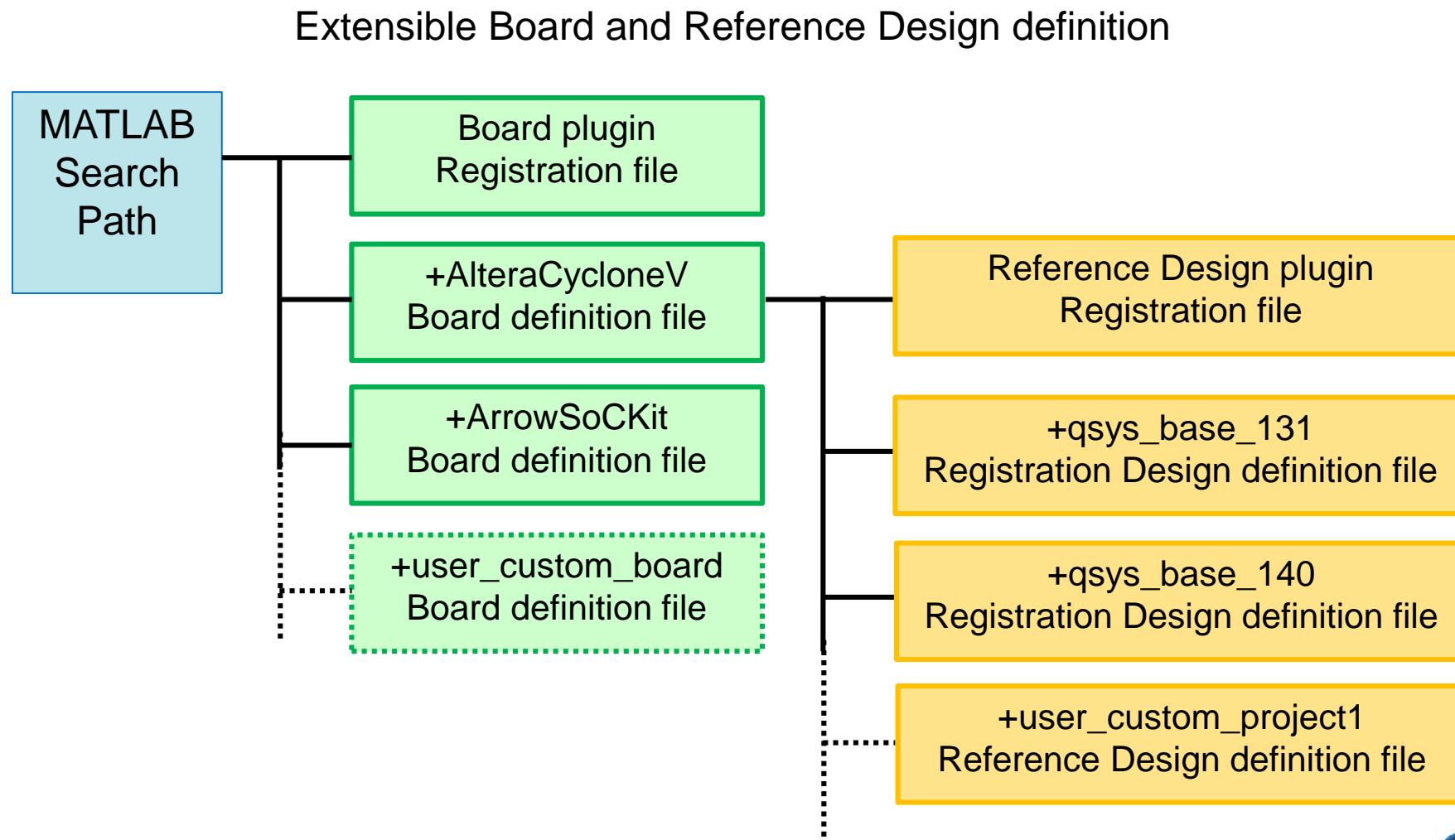

# Adding Support for Custom Altera SoC Boards and Reference Designs

# Reference Design Example

# Summary and Next Steps

## Altera SoC workflow support from MathWorks:

- Enables combined hardware/software code generation

- Provides predefined support for on Altera SoC and Arrow SoCKit development boards, and can be extended to other SoC boards.

## Learn more about Model-Based Design for Cyclone V SoCs

- Visit <http://www.mathworks.com/asdf>

- Visit [mathworks.com/alterasoc](http://mathworks.com/alterasoc)

- Contact us at [altera@mathworks.com](mailto:altera@mathworks.com) for instructions on how to get this workflow.

## Watch Altera/MathWorks webinar

### **Prototyping SoC-based Motor Controllers with MATLAB and Simulink**

- Features targeting field-oriented control algorithm into Altera's Drive-on-a-Chip Reference Design

The screenshot shows the MathWorks Hardware Support website. The main page features a banner for 'Altera SoC FPGA Support from Embedded Coder' with a 'Get Support Package Now' button. Below the banner, there's a section for 'Drive-On-Chip Reference Design' and a 'Videos and Webinars' section. The 'Videos and Webinars' section displays a video player for a webinar titled 'Prototyping SoC-based Motor Controllers with MATLAB and Simulink'. The video player shows a MATLAB/Simulink interface with a table of contents and a live video feed of two presenters. The video player also includes a 'Feedback' section and a 'Enlarge' button.