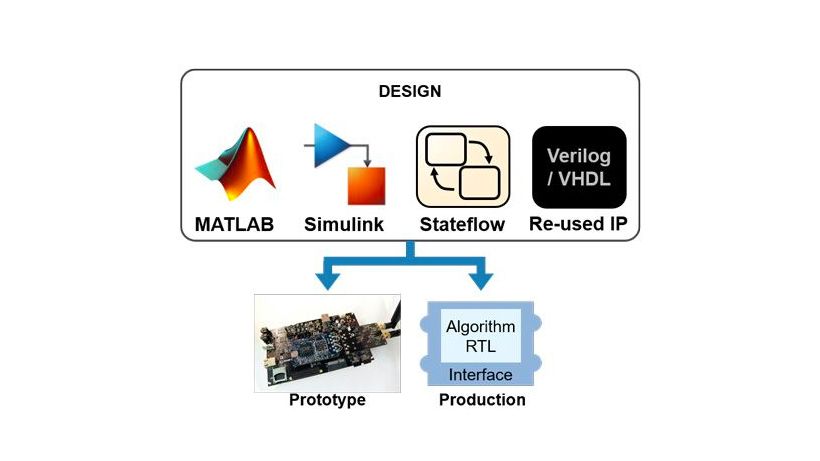

HDL Coder は、MATLAB 関数、Simulink モデル、および Stateflow チャートから移植や論理合成が可能な Verilog® および VHDL® コードを生成し、FPGA、SoC、および ASIC 向けの高位設計を可能にします。生成された HDL コードは、FPGA プログラミング、ASIC プロトタイピング、および量産設計に使用できます。

HDL Coder は、AMD®、Intel®、Microchip ボードでの生成されたコードのプロトタイピングを自動化し、ASIC および FPGA ワークフロー用の IP コアを生成するワークフロー アドバイザーを備えています。合成前に、速度および面積の最適化、クリティカルパスの強調表示、リソース使用量の推定の生成を行うことができます。HDL Coder は、Simulink モデルと生成された Verilog や VHDL コードとの間のトレーサビリティを提供し、DO-254 やその他の標準に準拠した高信頼性アプリケーションのコード検証を行うことができます。

高位ハードウェア設計

300 以上の HDL 対応 Simulink ブロックと MATLAB 関数から選択してサブシステムを設計し、Stateflow チャート、Simscape モデル、ディープラーニング ネットワークを追加できます。設計のハードウェア動作のシミュレーション、代替アーキテクチャの検討、固定小数点または浮動小数点データ型、あるいはその両方を組み合わせて、合成可能な VHDL または Verilog の生成を行います。

ドキュメンテーション | 例

設計の最適化

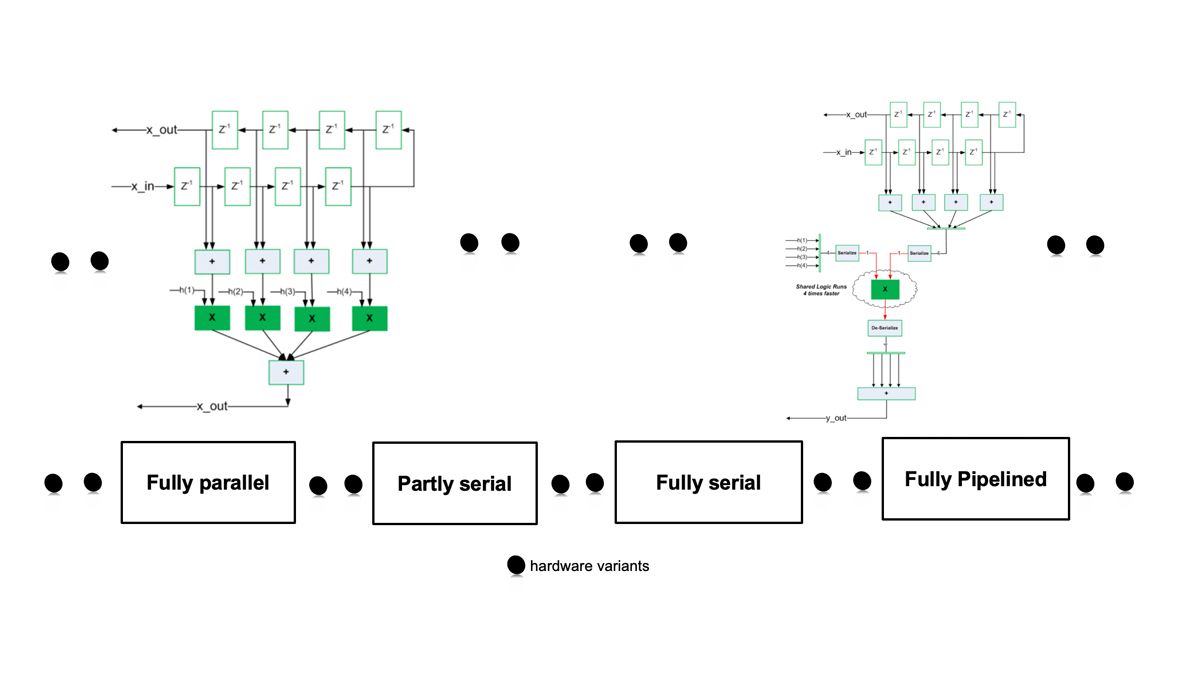

RTL 実装にコミットする前に、さまざまなハードウェア アーキテクチャと固定小数点の量子化オプションを検討します。リソース共有、パイプライン化、遅延の均衡化などの高位合成の最適化を使用して、ロジック、DSP、RAM などのデバイスリソースに効率的にマッピングします。

ドキュメンテーション | 例

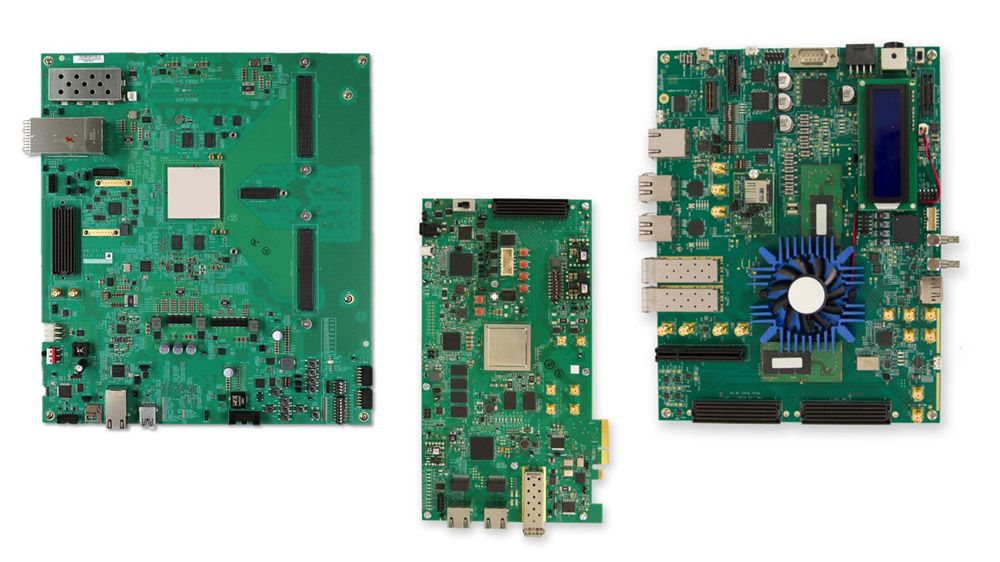

FPGA ベースのデバイス

AMD、Intel、および Microchip FPGA および SoC デバイスに効率的にマッピングする RTL を生成します。汎用ボード向けハードウェア サポート パッケージを使用して入出力をデバイスレベルの I/O および AXI レジスタにマッピングするか、独自のカスタムリファレンス設計を定義します。

ドキュメンテーション | 例

ASIC ワークフロー

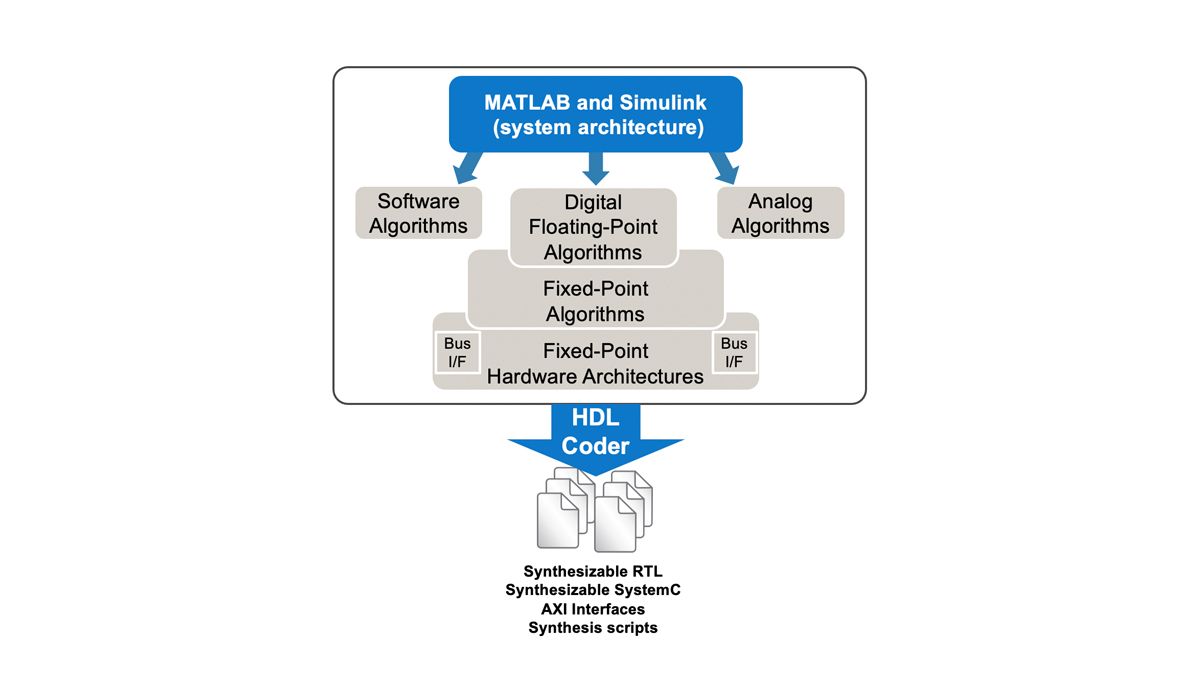

アナログ、デジタル、およびソフトウェアが混在するシステムのコンテキストにおいて、アーキテクチャと高位のハードウェア機能の設計および検証を行います。高い結果品質 (QoR) を持つ RTL や、Cadence® Stratus HLS で使用する合成可能な SystemC を生成します。

ドキュメンテーション | 例

アプリケーション開発

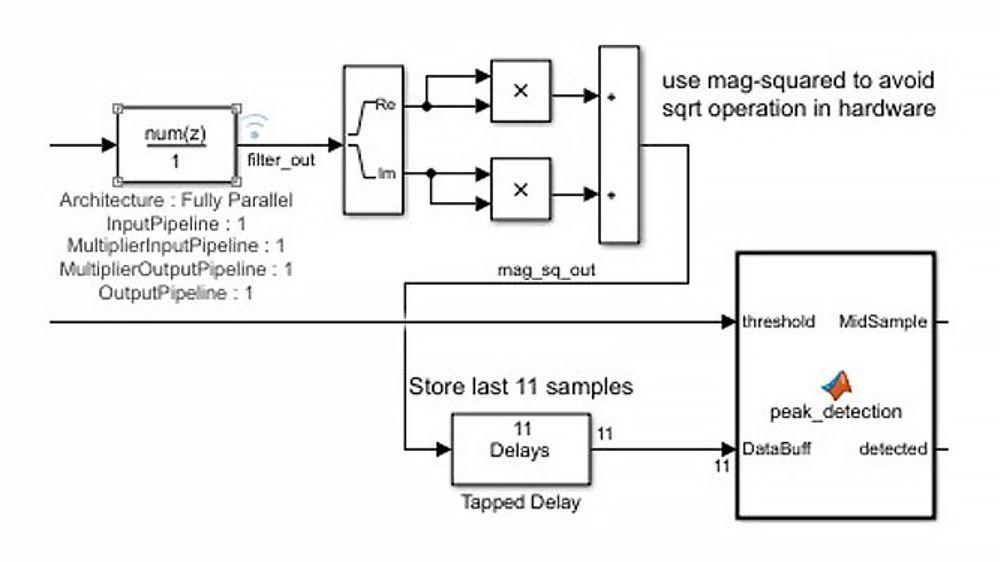

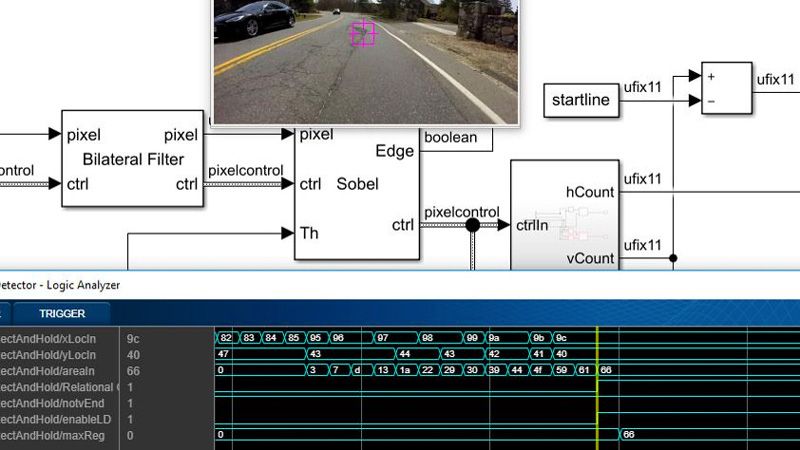

Wireless HDL Toolbox により、サブシステムやブロックを使用した通信アルゴリズムを設計します。また、Vision HDL Toolbox を使用して、画像処理アルゴリズムのストリーミング実装を開発します。複雑な低レイテンシのモーター制御システムを実装します。

ハードウェアの設計

ストリーミングデータに対して効率的に機能するアルゴリズムを開発します。HDL 対応の Simulink ブロック、カスタムの MATLAB Function ブロック、および Stateflow チャートを使用してハードウェア アーキテクチャの詳細を設計します。

リアルタイム シミュレーションおよびテスト

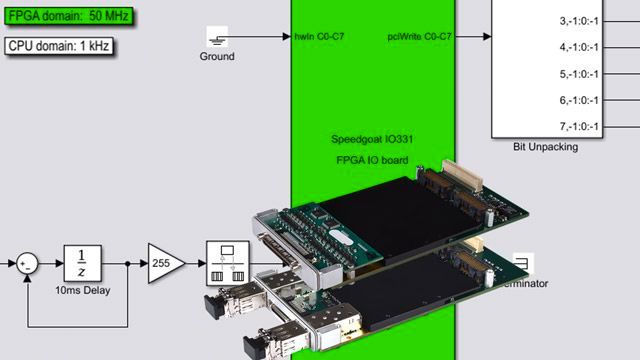

HDL ワークフロー アドバイザーを使用して Speedgoat のプログラム可能な FPGA I/O モジュールをターゲットとし、Simulink Real-Time を使用してシミュレーションするか、dSPACE および NI の FPGA I/O モジュールを追加して使用します。ネイティブ浮動小数点 HDL コードを生成し、高精度プロトタイピングのワークフローを簡略化します。

ドキュメンテーション | 例

早期検証

HDL Verifier とともに使用することで、生成した RTL がそのシステムコンテキストで必要に応じて機能することを確認します。主要な HDL シミュレーターとのコシミュレーションを使用して、生成された HDL を MATLAB および Simulink のテストベンチで検証します。FPGA インザループ テストを使用して、FPGA 開発ボードへの設計の実装を検証します。

ドキュメンテーション | 例

製品リソース:

「Simulink を使用することで、システムアーキテクトとハードウェア設計者の間のコミュニケーションがスムーズになります。Simulink という共通言語のおかげで、私たちは知識、アイデア、設計を交換することができます。Simulink と HDL Coder により、VHDL 構文とコーディングルールのチェックに時間をかけることなく、アルゴリズムの開発と、シミュレーションを介した設計の微調整に注力することができます。」

Marcel van Bakel, Philips Healthcare