Xilinx Vitis Model Composer

ザイリンクス FPGA 向けのビット精度およびサイクル精度のシミュレーションとコード生成のための Simulink 向け blockset

ハイライト

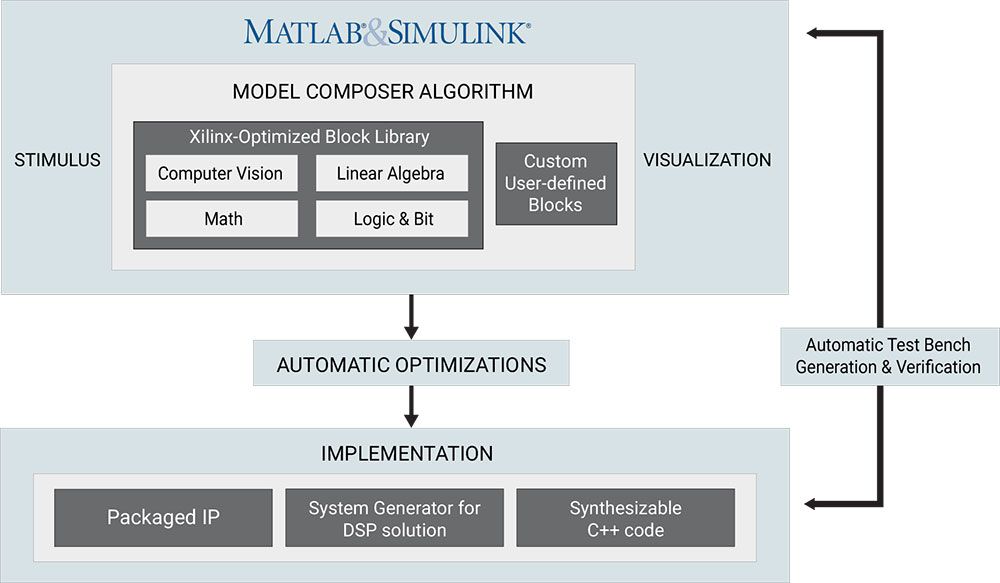

- AI エンジンとプログラマブル ロジックをターゲットとする最適化されたブロックを使用してデザインを作成

- シミュレーション結果を視覚化し、MALTAB® および Simulink® を使用して生成されたゴールデン リファレンスと比較

- AI エンジンブロックとプログラマブル ロジック (HLS、HDL) ブロックの協調シミュレーションをシームレスに実行

- デザインのコード (AI エンジンのデータフロー グラフ、RTL、HLS C++) とテストベンチを自動生成

- カスタムHLS、AI エンジン、RTL コードをブロックとしてインポート

説明

Xilinx Vitis™ Model Composer は、ザイリンクスの FPGA 向けの高性能 DSP システムを開発するための Simulink のプラグインです。設計者は、MATLAB、Simulink、およびザイリンクスのビット精度およびサイクル精度モデルのライブラリを使用して、システムの設計とシミュレーションを行うことができます。このツールはまた、ザイリンクスの最適化されたアルゴリズムにマッピングされた、合成可能なハードウェア記述言語 (HDL) コードを自動的に生成します。この HDL デザインは、ザイリンクスの FPGA や SoC への実装向けに合成することができます。これにより、設計者はシステムレベルの設計の抽象的な表現を定義し、この単一のソースコードをゲートレベルの表現に簡単に変換することができます。また、HDL テストベンチを自動的に生成し、実装時のデザイン検証を可能にします。

Vitis Model Composer は、スタンドアローンツールとしては提供されなくなった Xilinx System Generator for DSP の機能をすべて含んでいます。

Simulink と Xilinx FPGA によるプロトタイピングの詳細

以下のユーザー事例もご覧ください:

Xilinx, Inc.

2100 Logic Dr

San Jose, CA 95124-3450

UNITED STATES

電話: 408-559-7778

FAX: 408-626-6440

logicore@xilinx.com

https://www.xilinx.com

関連分野一覧: 組み込みハードウェア - MCU, DSP, FPGA, 通信システム, デジタル信号処理, 組み込みシステム, FPGA 設計, 画像処理、コンピューター ビジョン, 通信インフラ, 産業オートメーション、機械, 航空宇宙、防衛, 自動車