このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

サブシステム解析時の既存のカバレッジ データの使用

この例では、Simulink® Design Verifier™ において、連続時間閉ループ シミュレーション内の 1 つのサブシステムを解析のターゲットとし、そのサブシステムの未達カバレッジに対してテスト ケースを生成する方法を説明します。

この例では、最初に閉ループ シミュレーション モデルのサブシステムのカバレッジを測定します。Simulink Design Verifier は、サブシステムの未達カバレッジを達成させる新しいテスト ケースを検索します。

サブシステムのカバレッジの測定

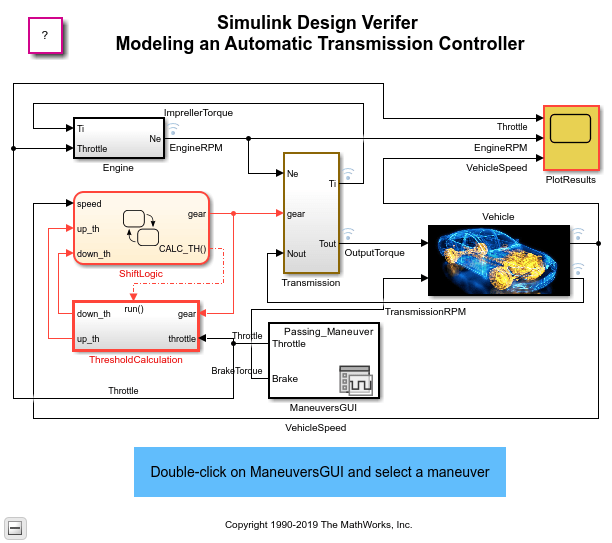

sldvdemo_autotrans モデルは閉ループ シミュレーション モデルです。サブシステム ShiftLogic は Stateflow® チャートで、このモデルのコントローラー部を表します。Signal Editor ブロック ManeuversGUI で設計されたテスト ケースは、閉ループ シミュレーションを駆動します。関数 cvtest および cvsim を使用して、閉ループ シミュレーション モデル内のこのサブシステムに対し達成されるモデル カバレッジを測定します。この例では、cvtest への入力を、モデル名ではなくサブシステムのパスとして指定することにより、そのサブシステムのみのカバレッジを測定します。また、cvsim の 2 番目の入力でモデルのシミュレーションを行う時間間隔を、ManeuversGUI ブロックの現在のペインの時間範囲から導かれる値に指定します。

関数 cvhtml は、ManeuversGUI ブロックで作成されたテスト ケースのシミュレーションの実行によって、87% の判定、67% の条件、33% の MCDC のカバレッジが達成されたことを示すレポートを生成します。

open_system('sldvdemo_autotrans'); open_system('sldvdemo_autotrans/ManeuversGUI'); test = cvtest('sldvdemo_autotrans/ShiftLogic'); test.settings.decision = 1; test.settings.condition = 1; test.settings.mcdc = 1; signalEditorBlock = sldvdemo_signaleditor_block('sldvdemo_autotrans'); signalEditorTime = sldvdemo_signaleditor_DataTime(signalEditorBlock); simulationStopTime = signalEditorTime{1,1}(end); existingCovData = cvsim(test,[0 simulationStopTime]); cvhtml('Existing Coverage', existingCovData);

未達カバレッジのテスト ケースの検出

テスト生成時に既存のカバレッジ データを使用するには、既存のカバレッジ データを .cvt カバレッジ データ ファイルとして保存します。既存のカバレッジ データを使用するには、Simulink Design Verifier のコンフィギュレーション パラメーターの [テスト生成] ペインで、[既存のカバレッジ データで条件が満たされているオブジェクティブを無視する] パラメーターを on に設定し、[カバレッジ データ ファイル] パラメーターにカバレッジ データ パスを指定します。

この例では、sldvrun の最初の入力で、解析するサブシステムを指定します。Simulink Design Verifier へのサブシステム解析の指示は、モデルのコントローラー部分を個別にテストする必要がある場合や、大きなモデルの解析をより小さく管理しやすい部分に分割する場合に有用です。

このレポートでもわかるように、Simulink Design Verifier は既存のカバレッジ ファイルでカバーされていないカバレッジ オブジェクティブのテスト ケースのみを検索します。サブシステム ShiftLogic の 4 つのカバレッジ オブジェクティブは非達成と証明されています。Stateflow チャート ShiftLogic の中のロジックは時相イベントを使用しており、このチャートはサンプル時間ごとに更新されるため時相条件の使用が満たされる必要があります。したがって、これは想定された結果です。また、サブシステム内のデッド コードは、そのサブシステムを含むモデルで必ずデッド コードになります。

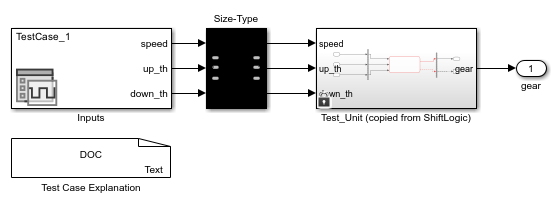

ハーネス モデルを生成するため、Simulink Design Verifier はサブシステム ShiftLogic の内容を、生成したテスト ケースを含む Signal Editor ブロックで接続されている Test Unit コンポーネントに抽出します。

cvsave('existingcov',existingCovData); opts = sldvoptions; opts.IgnoreCovSatisfied = 'on'; opts.CoverageDataFile = 'existingcov.cvt'; opts.ModelCoverageObjectives = 'MCDC'; opts.SaveHarnessModel = 'on'; opts.SaveReport = 'on'; [status, fileNames] = sldvrun('sldvdemo_autotrans/ShiftLogic',opts,true); [~, harnessModel] = fileparts(fileNames.HarnessModel); open_system(harnessModel);

クリーン アップ

デモを完了するには、すべてのモデルを閉じて保存されたカバレッジ データ ファイルを削除します。

close_system('sldvdemo_autotrans'); close_system(fileNames.ExtractedModel,0); close_system(fileNames.HarnessModel,0); delete('existingcov.cvt');