このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

スプリアスフリー ダイナミック レンジ (SFDR) の測定

この例は、固定小数点演算で実装されたデジタルダウン コンバーター (DDC) の数値制御発振器 (NCO) を解析する方法を示しています。例では、NCO のスプリアス フリー ダイナミック レンジ (SFDR) を測定すると共に、位相ディザーの追加による影響を調べます。ディザーのビット数は、ハードウェア実行の選択に影響します。例では、ノイズ フロア レベル、スプリアスの影響およびディザーのビット数の間のトレードオフを示します。例に含まれる DDC は、GSM 仕様を満たすよう設計されており、Graychip 4016 をモデル化します。

はじめに

数値制御発振器 (NCO) は、正弦波信号を効率的に生成する手段として、可変周波数で連続位相の正弦波信号が必要な場合に役立ちます。

DDC は、デジタル無線の主要コンポーネントです。これはデジタル無線の高入力サンプル レートをより低いサンプル レート (基底域) に変換し、処理をより効率化、容易化します。使用する DDC の入力レートは 69.333 MHz であり、GSM 仕様に従ってこのレートを変換し、270.833 kHz に引き下げます。

DDC は、NCO と、入力信号を基底域に直交ダウン コンバートする混合器で構成されます。次次に、カスケード接続積分器櫛形 (CIC) によって基底域信号がローパス フィルター処理され、2 つの FIR 間引きフィルターと共に、信号がダウンサンプリングされ、目的の低サンプル レートになります。これで、次の処理に移行できます。最終段階では、用途に応じて、目的のサンプル レートを達成するために信号を内挿または間引きするリサンプラーを使用する場合もあります。リサンプラーを使用することで、フィルター処理をさらに実行できます。典型的な DDC については、以下のブロック線図を参照してください。Simulink® では複素信号を処理するため、I チャネルと Q チャネルを別々に処理する必要はありません。

この例では NCO の解析を主に取り上げますが、3 段マルチレート固定小数点フィルター チェインおよび HDL コード生成の設計を取り上げたデジタル ダウン コンバーターのフィルター チェインの実装という例が、DSP System Toolbox™ から利用できます。

数値制御発振器

DDC のデジタル ミキサー セクションには、乗数およびラジオのチャネルの選択と調整を行う NCO が含まれます。ミキサーは、基本的に正弦-余弦発生器であり、正弦と余弦の組み合わせごとに複素数値を作成します。典型的な NCO には 4 つのコンポーネントがあります。すなわち、位相アキュムレータ、位相加算器、ディザー発生器、および正弦-余弦ルックアップ テーブルです。

以下のブロック線図は、Simulink でモデル化された典型的な NCO 回路で、Graychip データ シートの図に似ています。

open_system('ddcncomodel')

NCO の位相アキュムレータは、入力周波数に基づいて、正弦-余弦ルックアップ テーブルで使用される値を生成します。位相加算器は、位相アキュムレータの出力を変調する位相オフセットを指定します。ディザー発生器によって生じる位相のディザリングは、振幅の量子化ノイズを軽減し、NCO の SFDR を改善します。Sine/Cosine Lookup ブロックは、実際の複素正弦波信号を生成し、その出力は変数 nco_nodither に保存されます。

Graychip の調整周波数は、チップのクロック レートに対して正規化された値として指定されます。したがって、調整周波数が F の場合、正規化周波数は F/Fclk です。ここで、Fclk はチップのクロック レートです。位相オフセットは、ラジアン単位で指定され、範囲は 0 ~ 2pi です。この例では、正規化された調整周波数は 5/24 に設定され、位相オフセットは 0 に設定されています。調整周波数は 32 ビット ワードとして指定し、位相オフセットは 16 ビット ワードとして指定します。

NCO は、固定小数点演算を使用して実装されるため、望ましくない振幅の量子化の影響を受けます。このような数値の歪みは、語長が有限であるために生じます。基本的に、正弦波を量子化すると、時間領域で累積的、確定的、および周期的な誤差が発生します。このような誤差は、周波数領域のラインスペクトルまたはスパーとして現れます。対象の信号のピークから最大スパーまでの減衰量が SFDR です。

Graychip の SFDR は 106dB ですが、GSM 仕様では、SFDR が 110dB より大きい必要があります。SFDR を改善する方法は複数あり、位相ディザーを NCO に加えてその影響を調べます。

Graychip の NCO には、基本的に発振器の出力純度を改善するために使用される乱数整数発生器である位相ディザー発生器が含まれています。ディザリングによって、意図しない量子化ノイズ (スペクトルの "スパイク" の原因で、SFDR を低下させる) の周期性が広範囲のスペクトルに広がり、望ましくないスペクトル ピークを効果的に減少できます。ただしエネルギー保存が適用されるため、この広がりによってノイズ フロア全体が効果的に上昇します。すなわち、ディザリングはある程度までは SFDR に効果的です。

NCO モデルを実行し、MATLAB ワークスペースの出力を解析します。このモデルでは、ディザリングは使用しません。

sim('ddcncomodel') whos nco*

Name Size Bytes Class Attributes nco_nodither 1x1x20545 328720 double complex

次のプロットは、NCO 出力の最初の 128 のサンプルの実数部で、変数 nco_nodither に保存されます。

plot(real(squeeze(nco_nodither(1:128)))) grid title('Real Part of NCO Output - No Dithering') ylabel('Amplitude') xlabel('Samples')

NCO 出力の SFDR

NCO の出力の SFDR を見てみましょう。

NCO 出力の SFDR を計算し、プロットします。

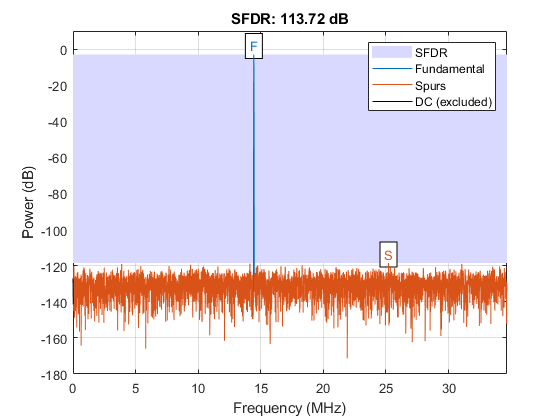

Fs = 69.333e6; sfdr(real(nco_nodither),Fs);

予想どおり、パワー スペクトル プロットは、14.44 MHz でピークを示しています。すなわち、NCO の調整周波数は 5/24*Fs = 14.444 MHz です。

ただし、SFDR は約 106.17 dB で、GSM 仕様を満たすには高過ぎ、110 dB 以上にする必要があります。このダイナミック レンジは位相ディザリングにより改善できます。

ディザリングの効果の調査

ディザーを NCO に追加した場合の効果を調査するために、上記の NCO 回路がサブシステムでカプセル化され、3 回複製されています。NCO ごとに異なる量のディザーが選択されています。NCO では 1 ~ 19 ビットの範囲のディザーを指定できますが、このデモではいくつかの値を指定してみます。このモデルを実行すると、追加されたディザーの量に基づいて 3 つの異なる NCO 出力が生成されます。

open_system('ddcncowithdithermodel')

このシミュレーションを実行すると、MATLAB ワークスペースで 3 つの信号が生成され、これまでに定義したスペクトル解析アルゴリズムを使用して、解析できます。このシミュレーションは、モデルまたはコマンド ラインから sim コマンドを使用して実行できます。

sim('ddcncowithdithermodel')

シミュレーションが完了すると、NCO の出力である信号が示されます。各信号は異なる量のディザリングを示しています。

whos nco*

Name Size Bytes Class Attributes nco_dither3 1x1x20501 328016 double complex nco_dither5 1x1x20501 328016 double complex nco_dither7 1x1x20501 328016 double complex nco_nodither 1x1x20545 328720 double complex

3 ビットのディザリングを追加した後で、SFDR を計算してプロットします。

figure sfdr(real(nco_dither3),Fs)

ans = 107.6285

3 つのディザーのビットが追加されたため、最大スパーは約 -112dB です。SFDR は 107.63dB です。まだ GSM 仕様を満たしていません。

ここで、5 ビットのディザリングを追加します。

figure sfdr(real(nco_dither5),Fs)

ans = 123.4065

5 ビットのディザーが追加されたため、最大スパーは約 -127dB です。

SFDR は 123.41dB で、GSM 仕様を超えています。

大きいディザーを追加するとよい結果が得られたため、7 ビットのディザリングを追加します。

figure sfdr(real(nco_dither7),Fs)

ans = 113.7189

計算後の SFDR が 113.72 dB に低下していることに注目してください。これは、ディザリングによって生成された広帯域ノイズがスプリアス成分の電力を上回り始めたためです。

7 ビットのディザリングを使用すると GSM 仕様は満たされますが、5 ビットのディザリングを使用したときと比較すると効果的ではありません。

結果の比較

NCO 出力ごとのディザリング量に対する NCO 出力ごとの SFDR を表にします。

Number of Spur Free Dynamic Dither bits Range(dB)

0 106.17

3 107.63

5 123.41

7 113.72

まとめ

この例では、GSM アプリケーションのデジタルダウンコンバーターで使用される NCO の出力を解析しました。SFDR (最大スパーと対象の信号のピークの差) の測定にはスペクトル解析を使用しました。スパーは、量子化の影響による確定的、周期的な誤差です。また、この例では、NCO におけるディザーを追加した場合の効果を調査し、純度を改善するため乱数データを NCO に追加しました。その結果、5 ビットのディザリングを使用すると最大の SFDR を達成できることがわかりました。