このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

サポートされているデータ型

MATLABまたはSimulinkに送信するための HDL データの変換

HDL アプリケーションが HDL データをMATLAB®関数またはSimulink®ブロックに送信する必要がある場合は、最初にデータをでサポートされる型に変換する必要がある場合があります。 MATLABおよびHDL Verifier™ソフトウェア。

HDL モデルのMATLAB関数またはSimulinkブロックをプログラムするには、アプリケーションで必要な型変換を理解する必要があります。また、使用している HDL とMATLABで使用される配列インデックス付け規則の違いに対処する必要がある場合もあります (次のセクションを参照)。

関数に渡される引数のデータ型によって、次のことが決まります。

データを操作する前に必要な変換の種類

データを HDL シミュレーターに返すために必要な変換の種類

次の表は、 HDL Verifierソフトウェアが、サポートされているVHDL®データ型を、型がスカラーか配列かに基づいてMATLAB型に変換する方法をまとめたものです。

VHDL からMATLABデータ型への変換

| VHDL種類... | スカラー変換すると... | 配列が次のように変換されると... |

|---|---|---|

STD_LOGIC、STD_ULOGIC、BIT | 目的の論理状態の文字リテラルに一致する文字。 | |

STD_LOGIC_VECTOR、STD_ULOGIC_VECTOR、BIT_VECTOR、SIGNED、および UNSIGNED | 1 文字あたり 1 ビットの文字の列ベクトル ( VHDL HDL シミュレーターの変換で定義)。 | |

STD_LOGIC_VECTOR、 STD_ULOGIC_VECTOR、 BIT_VECTOR、 SIGNED、およびUNSIGNEDの配列 | VHDLポート サイズと同等のサイズを持つ文字の配列 (上で定義したとおり)。 | |

INTEGER および NATURAL | int32 を入力します。 | int32ポート サイズと同等のサイズを持つ、タイプVHDL の配列。 |

REAL | double を入力します。 | double VHDL の配列。 |

TIME | 秒単位の時間値にはdoubleと入力し、シミュレータの時間増分を表す値には int64と入力します ( TGの'time'オプションの説明を参照してください) hdldaemon)。 | doubleポート サイズと同等のサイズを持つint64VHDLの配列。 |

| 列挙型 | MATLABラベルまたは文字列リテラルのVHDL表現を含む文字ベクトルまたは string スカラー。たとえば、ラベルhighは'high'に変換され、文字リテラル'c'は'''c'''に変換されます。 | 定義された列挙型のラベルに等しい各要素を含む文字ベクトルの cell 配列または文字列配列。各要素は、MATLAB VHDL 表現です。たとえば、ベクトル(one, '2', three)は、列ベクトル['one'; '''2'''; 'three']に変換されます。文字リテラルのみを含み、型STD_LOGIC_VECTOR、 STD_ULOGIC_VECTOR、 に示されている文字のベクトルまたは配列に変換されるユーザー定義の列挙型。 BIT_VECTOR、 SIGNED、およびUNSIGNED。 |

次の表は、 HDL VerifierソフトウェアがサポートされているVerilog®データ型をMATLAB型に変換する方法をまとめたものです。ソフトウェアは、 Verilogに対して最大 128 ビットのパック配列をサポートします。

VerilogからMATLABデータ型への変換

| Verilog種類... | に変換します... |

|---|---|

wire, reg | 目的の論理状態 (ビット) の文字リテラルに一致する文字または文字の列ベクトル。 |

次の表は、 HDL Verifierソフトウェアがサポートされている SystemVerilog データ型をMATLAB型に変換する方法をまとめたものです。このソフトウェアは、SystemVerilog の最大 128 ビットのパック配列をサポートします。

SystemVerilog からMATLABへのデータ型変換

| SystemVerilog タイプ... | に変換します... |

|---|---|

wire, reg, logic | 目的の論理状態 (ビット) の文字リテラルに一致する文字または文字の列ベクトル。 |

integer | 目的の論理状態 (ビット) の文字リテラルに一致する文字の 32 要素の列ベクトル。出力のみでサポートされます。 |

bit | boolean/ufix1 |

byte | int8/uint8 |

shortint | int16/uint16 |

int | int32 |

longint | int64/uint64 |

real | double |

packed array |

|

a For currently supported packed array input or output to the HDL Cosimulation block, the total number of bits in the packed array has a 128 upper limit. | |

メモ

SystemVerilog サポートには、上記のタイプの信号が含まれます。次の SystemVerilog タイプはサポートされていません。

解凍された配列と多次元配列

shortrealシステム Verilog タイプSystemVerilog 集計タイプ (

structやunionなど)SystemVerilog インターフェイス

MATLABと HDL のビット ベクトル インデックスの違い

HDL では、MSB-0 または LSB-0 の番号付けでビット ベクトルを定義できる柔軟性があります。MATLABでは、ビットベクトルは常に LSB-0 番号付けとみなされます。データの破損を防ぐために、HDL インターフェイスには LSB-0 インデックスを使用することをお勧めします。

VHDL で論理ベクトルを次のように定義すると、

signal s1 : std_logic_vector(7 downto 0);

または、Verilog では次のようになります。

reg[7:0] s1;

これは、 s1[7] を MSB として、 MATLABの int8 にマッピングされます。あるいは、VHDL ロジック ベクトルを次のように定義するとします。

signal s1 : std_logic_vector(0 to 7);

または、Verilog では次のようになります。

reg[0:7] s1;

これは、 s1[0] を MSB として、 MATLABの int8 にマッピングされます。

MATLABと HDL の配列インデックス付けの違い

多次元配列では、基盤となる同じ OS メモリ バッファーが、 MATLABおよび HDL シミュレーターの異なる要素にマップされます (このマッピングは、同じ配列の要素に名前を付けるために異なる言語が提供する異なる方法を反映しているだけです)。matlabtb関数とmatlabcp関数の両方を使用する場合は、両方のアプリケーションで一貫して値を割り当てて解釈するように注意してください。

HDL では、多次元配列は次のように宣言されます。

type matrix_2x3x4 is array (0 to 1, 4 downto 2) of std_logic_vector(8 downto 5);

次のようなメモリ レイアウトがあります。

bit 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 - dim1 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 dim2 4 4 4 4 3 3 3 3 2 2 2 2 4 4 4 4 3 3 3 3 2 2 2 2 dim3 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5

これと同じレイアウトは、次のMATLAB 4x3x2 マトリックスに対応します。

bit 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 - dim1 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 dim2 1 1 1 1 2 2 2 2 3 3 3 3 1 1 1 1 2 2 2 2 3 3 3 3 dim3 1 1 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2 2 2 2 2 2 2 2

したがって、H が HDL 配列、M がMATLAB行列の場合、次のインデックス付きの値は同じになります。

b1 H(0,4,8) = M(1,1,1) b2 H(0,4,7) = M(2,1,1) b3 H(0,4,6) = M(3,1,1) b4 H(0,4,5) = M(4,1,1) b5 H(0,3,8) = M(1,2,1) b6 H(0,3,7) = M(2,2,1) ... b19 H(1,3,6) = M(3,2,2) b20 H(1,3,5) = M(4,2,2) b21 H(1,2,8) = M(1,3,2) b22 H(1,2,7) = M(2,3,2) b23 H(1,2,6) = M(3,3,2) b24 H(1,2,5) = M(4,3,2)

このインデックス付けを N 次元に拡張できます。一般に、左から右に番号が付けられている場合、次元は逆になります。HDL の右端の次元は、 MATLABの左端の次元に対応します。

配列のインデックス付け - 列メジャー

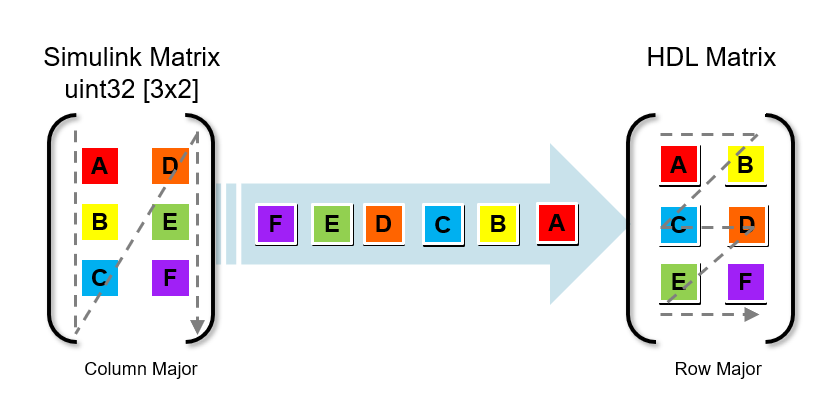

SystemVerilog DUT を使用してSimulinkコシミュレーションを実行し、DUT にunpacked arrayポートが含まれている場合、 HDL Verifier が配列のインデックスを作成することに注意してください。列のメジャーオーダー。たとえば、3x2 HDL 行列の場合、次のように定義されます。

logic [31:0] In1 [0:2][0:1]

この図では、 Simulink行列に列優先でインデックスを付けると、要素が次の順序で列ごとに読み取られます。

A, B, C, D, E, F

m1 がSimulink行列で、 m2が HDL 行列の場合、次のインデックス付きの値は同じになります ( Simulinkインデックス モードは0-baseです):m1(0,0) = m2(0,0) = A m1(1,0) = m2(0,1) = B m1(2,0) = m2(1,0) = C m1(0,1) = m2(1,1) = D m1(1,1) = m2(2,0) = E m1(2,1) = m2(2,1) = F

操作のためのデータの変換

シミュレーションMATLAB関数が HDL シミュレーターから受け取るデータをどのように使用するかによっては、データを操作する前に、データを別の型に変換する関数をコーディングする必要がある場合があります。次の表に、そのような変換が必要になる状況を示します。

必要なデータ変換

| この機能が必要な場合は... | 説明 |

|---|---|

double以外の型として受け取った数値データを計算します | 計算を実行する前に、 datas(inc+1) = double(idata); |

| 標準ロジックまたはビット ベクトルを符号なし整数または正の 10 進数に変換します |

uval = mvl2dec(oport.val) この例では、標準ロジックまたはビット ベクトルが文字リテラル

この関数の詳細については、 |

| 標準ロジックまたはビット ベクトルを負の 10 進数に変換します | 次の suval = mvl2dec(oport.val, true); この例では、標準ロジックまたはビット ベクトルが文字リテラル |

例

次のコードの抜粋は、コールバックに渡されるデータのデータ型変換を示しています。

InDelayLine(1) = InputScale * mvl2dec(iport.osc_in',true);

この例では、次のように all関数を使用して、 VHDLタイプ STD_LOGIC およびSTD_LOGIC_VECTORのポート値をテストします。 :

all(oport.val == '1' | oport.val == '0')

この例では、すべての要素がTrue '1' の場合、 '0'を返します。

HDL シミュレータに返すためのデータの変換

シミュレーションMATLAB関数が HDL シミュレーターにデータを返す必要がある場合は、最初にデータをHDL Verifierソフトウェアでサポートされている型に変換する必要がある場合があります。次の表は、 VHDLおよびVerilogでそのような変換が必要となる状況を示しています。

メモ

データ値が HDL シミュレーターに返されるとき、char 配列のサイズは、該当する場合は先行ゼロを含めて HDL 型と一致する必要があります。以下に例を示します。

oport.signal = dec2mvl(2)

signal がHDL の 2 ビット型である場合にのみ機能します。HDL タイプがそれ以外の場合は、2 番目の引数を「必ず」指定する必要があります。

oport.signal = dec2mvl(2, N)

ここで、N は HDL データ型のビット数です。

VHDL HDL シミュレーターの変換

| 次のタイプの IN ポートにデータを返すには... | 説明 |

|---|---|

STD_LOGIC、STD_ULOGIC または BIT | 目的の論理状態の文字リテラルに一致する文字としてデータを宣言します。 iport.s1 = 'X'; %STD_LOGIC iport.bit = '1'; %BIT |

STD_LOGIC_VECTOR、STD_ULOGIC_VECTOR、BIT_VECTOR、SIGNED または UNSIGNED | データを、1 文字あたり 1 ビットの文字の列ベクトルまたは行ベクトル (上記で定義したとおり) として宣言します。以下に例を示します。 iport.s1v = 'X10ZZ'; %STD_LOGIC_VECTOR iport.bitv = '10100'; %BIT_VECTOR iport.uns = dec2mvl(10,8); %UNSIGNED, 8 bits |

STD_LOGIC_VECTOR、 STD_ULOGIC_VECTOR、 BIT_VECTOR、 SIGNED、またはUNSIGNEDの配列 | データを、 VHDLポート サイズと同等のサイズを持つ文字型の配列として宣言します。MATLABと HDL の配列インデックス付けの違いを参照してください。 |

INTEGERまたは NATURAL | データを、 iport.int = int32(1:10)'; |

REAL | データを、 iport.dbl = ones(2,2); |

TIME | VHDL iport.t1 = int64(1:10)'; %Simulator time

%increments

iport.t2 = 1e-9; %1 nsec

|

| 列挙型 | データを、定義された列挙型のラベルと等しい各要素を持つ、スカラー端子の場合は文字ベクトルまたは文字列スカラーとして、または文字ベクトルの cell 配列または配列端子の場合は文字列配列として宣言します。 iport.char = {'''A''', '''B'''}; %Character

%literal

iport.udef = 'mylabel'; %User-defined label

|

| 標準ロジックまたはビット表現の文字配列 |

oport.slva =dec2mvl([23 99],8)'; |

Verilog HDL シミュレーターの変換

データをinputタイプのポートに返すには... | 説明 |

|---|---|

reg, wire | データを、目的の論理状態の文字リテラルに一致する文字または文字の列ベクトルとして宣言します。以下に例を示します。 iport.bit = '1'; |

HDL シミュレーターの SystemVerilog 変換

データをinputタイプのポートに返すには... | 説明 |

|---|---|

reg, wire, logic | データを、目的の論理状態の文字リテラルに一致する文字または文字の列ベクトルとして宣言します。以下に例を示します。 iport.bit = '1'; |

integer | データを、1 文字あたり 1 ビットの文字の 32 要素の列ベクトル (上で定義したとおり) として宣言します。 |

パック配列は 128 ビットまでサポートされます。

メモ

SystemVerilog サポートには、上記のタイプのスカラー信号のみが含まれます。次の SystemVerilog タイプはサポートされていません。

配列と多次元配列

shortrealシステム Verilog タイプSystemVerilog 集計タイプ (

structやunionなど)SystemVerilog インターフェイス

Simulinkによる Wide HDL ポートの処理

HDL モジュールに 128 ビットより広いポートがある場合、 Simulink はこのポートを表すポートのベクトルを作成します。コシミュレーション ウィザードは、HDL ポートのサイズを推測します。次に、 HDL CosimulationブロックでSimulink のワード長パラメーターを設定できます。

入力ポートの場合 — Simulinkポートの寸法は、駆動信号のデータ型によってコンパイル時に決定されます。以下に例を示します。

HDL ワード長 = 150 およびSimulinkワード長 = 50 の場合、 HDL Verifier、データ幅 50 ビット、サイズ 3 のSimulinkポートが許可されます ( など)。 $

sfix50(3)またはufix50(3)。HDL ワード長 = 140 およびSimulinkワード長 = 50 の場合、 HDL Verifier はSimulinkの 150 ビットを 140 ビットの HDL にパックします。 HDL Verifier は、最後のワードの 10 個の最上位ビット (MSB) を無視します。

出力ポート用

HDL Verifier は、出力ポートを表すポートのベクトルを作成します。以下に例を示します。

HDL ワード長 = 150 およびSimulinkワード長 = 50 の場合、 HDL Verifier はデータ幅 50 ビットのSimulinkポートを作成します。たとえば、

sfix50(3)やufix50(3)などです。HDL ワード長 = 150 およびSimulinkワード長 = 60 の場合、 HDL Verifier は、データ幅 60 のSimulinkポート (

sfix60(3)など) を作成します。 $またはufix60(3)。HDL ワードには 150 ビットしかなく、 Simulinkポートには 180 ビットが必要なため、30 ビットが埋め込まれるか符号拡張されます。HDL ワード長 = 140 およびSimulinkワード長 = 50 の場合、HDL 出力の 50 ビットごとがSimulinkワードとして表されます。最後のSimulinkワードの MSB 10 は未使用であり、Signパラメーターに従って拡張されます。

SystemVerilog のアンパック配列に対するSimulink のサポート

既存の HDL DUT がある場合 — コシミュレーション ウィザードを使用して、インターフェイス上にアンパックされた配列を含む SystemVerilog DUT をインポートする場合、 HDL Verifier は次の規則に従います。

入力端子の場合、 HDL CosimulationブロックはSimulinkからの行列データを受け入れることができます。

出力端子の場合、 HDL Cosimulationブロックはデータのフラット ベクトルを出力します。

HDL Verifier は、配列と行列を列優先順序で解釈します。詳細については、配列のインデックス付け - 列メジャーを参照してください。

たとえば、SystemVerilog DUT が 2 行 5 列のアンパック配列入力および出力ポートを使用してこのインターフェイスを定義している場合、次のようになります。

module myDUT

(input logic clk,

input logic clk_en,

input logic[31:0] In1[0:1] [0:4],

output logic[31:0] Out1[0:1] [0:4],

output logic ce_out);これで、 Simulinkなど、 int32の 10 個の要素を使用して入力を駆動するint32 [2x5]テストベンチを作成できるようになりました。出力ポートは、10 個の要素のフラット配列int32 [10x1]にマップされます。

![HDL Cosimulation block showing input port with data type int32[2x5] and output port of type int32(10)](unpackedarray0.png)

HDL DUT を生成するとき — HDL ワークフロー アドバイザーを使用して SystemVerilog DUT を生成するとき、 HDL Verifier はDUT インターフェイス上の 1 次元配列 (ベクトル) のみのコシミュレーション テストベンチ モデルを生成できます。 。 (HDL Coder)

Vivado®シミュレータは、アンパックされた配列をサポートしていません。

Verilog および SystemVerilog 列挙型のSimulinkサポート

既存の HDL DUT がある場合 — コシミュレーション ウィザードを使用して、インターフェイス上にタイプenumのポートを含む DUT をインポートすると、 HDL Verifierは固定小数点論理ベクトルにポートします。その論理ベクトルのサイズは、enum型を表すために必要なビット数によって決まります。

たとえば、SystemVerilog DUT がBasicColors入出力ポートを使用してこのインターフェイスを定義している場合、ポートはufix2タイプの入力または出力にマップされます。

typedef enum logic [1:0] {

Red,

Yellow,

Blue

} t_BaiscColors;

module scalarEnums

( input t_BasicColors In1,

output t_BasicColors Out1);

HDL DUT を生成するとき — HDL ワークフロー アドバイザーを使用して Verilog または SystemVerilog DUT を生成するとき、 HDL Verifier はコシミュレーション テストベンチ モデルを生成し、 Simulink.IntEnumTypeを使用するように型を変換します。 DUT に一致する$$データ型。 (HDL Coder)Simulink列挙の詳細については、 列挙型のコードの生成 (Simulink)を参照してください。

VHDL は列挙型をサポートしません。

参考

HDL Cosimulation | hdlverifier.HDLCosimulation |