このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

HDL Cosimulation

Simulinkを HDL シミュレータに接続して HDL 設計をコシミュレーションする

ライブラリ:

HDL Verifier /

For Use with Cadence Xcelium

HDL Verifier /

For Use with Mentor Graphics ModelSim

HDL Verifier /

For Use with Xilinx Vivado Simulator

説明

HDL Cosimulationブロックは、HDL シミュレーターでのシミュレーション中に HDL モデルに入力信号を適用したり、HDL モデルから出力信号を読み取ったりすることにより、ハードウェア コンポーネントを協調シミュレーションします。Cosimulation Wizard を使用して、このブロックを構成および生成します。Vivado®シミュレータを使用して協調シミュレーションを行う場合は、まず Cosimulation Wizard を使用してこのブロックを生成する必要があります。ModelSim®またはXcelium™と協調シミュレーションする場合、オプションでウィザードをバイパスしてブロックを直接構成できます。

ブロックで次のオプションを構成できます。

HDL モジュールの信号 (内部信号を含む) に対応するブロックの入力ポートと出力ポートのマッピング。各出力ポートのサンプル時間を指定する必要があります。オプションで、各出力ポートのデータ型を指定できます。 Vivadoコシミュレーションは、内部信号のマッピングをサポートしていません。

シミュレータ間でデータを交換するために使用される通信の種類と通信設定。

Simulink®と HDL シミュレーターのシミュレーション時間の単位間のタイミング関係。

モデルに適用する立ち上がりエッジまたは立ち下がりエッジのクロック。各クロック信号の周期を指定できます。

シミュレーションの前後に実行する Tcl コマンド。

このブロックを入力ポートまたは出力ポートのみで構成することにより、このブロックを使用してソース デバイスまたはシンク デバイスをモデル化できます。

Simulinkコード生成との互換性

このブロックは、 HDL Coder™による HDL コード生成に参加します。コーダーは、手動で記述されたまたは従来の HDL コードへのインターフェイスを生成します。Simulink Coder™による C コード生成には参加しません。

端子

ブロックに表示されているポートは、HDL シミュレーターで実行されている HDL デザインからの信号に対応します。Portsタブには、ポートに対応する HDL 信号が表示されます。

XceliumまたはModelSimシミュレーターを使用する場合、ブロックパラメーターを変更することで、端子を追加および削除し、そのデータ型とサンプル時間を構成できます。Auto Fillボタンを使用して、HDL シミュレーターへのポート情報要求を通じてテーブルに値を入力します。この要求は、 HDL シミュレーターで実行されている HDL デザインからポート名と情報を返します (コシミュレーション ウィザードを使用してブロックを生成した場合、この手順は必要ありません)。HDL シミュレーターから信号情報を取得するを参照してください。

HDL Cosimulationブロックを構成するときに指定するすべての信号には、HDL シミュレーターで読み取り/書き込みアクセスが必要です。詳細については、HDL シミュレータの製品ドキュメントを参照してください。

入力

HDL_input_port_name — Simulinkから HDL シミュレーターに渡された信号

スカラー | ベクトル

ブロック上のポートは、HDL デザインのポートに対応します。「Ports 」タブでポートを追加または削除します。

データ型: int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | Fixed-point

出力

HDL_output_port_name — HDL シミュレータからSimulinkに渡される信号

スカラー | ベクトル

ブロック上のポートは、HDL デザインのポートに対応します。「Ports 」タブでポートを追加または削除します。

データ型: int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | Fixed-point

パラメーター

Block Info — Vivado コシミュレーションのブロック情報

ブロック生成設定

この パラメーター は読み取り専用です。

このセクションには、コシミュレーション ウィザードを使用してこのブロックを生成した後の情報が表示されます。次の項目が表示されます。

HDL シミュレーター – Vivadoシミュレーター

HDL デザイン ライブラリ – HDL ライブラリ ファイルの場所

HDL 言語 – VHDL または Verilog

HDL 時間精度 – HDL 設計の時間精度

HDL 波形ファイル – 波形ファイルの名前とパス

Vivadoシミュレーターのコシミュレーション ブロックを生成する場合、ブロック マスクを使用してポート、クロック、リセット、または時間精度の名前と方向を変更することはできません。これらの項目を変更するには、コシミュレーション ウィザードを開いてブロックを再生成します。

依存関係

このパラメーターは、 Vivadoコシミュレーションを使用する場合にのみ表示されます。

端子

Enable direct feedthrough — 代数ループ警告を回避する

true (既定値) | false

モデルに純粋な組み合わせパスが含まれている場合に発生する、コシミュレーションとSimulinkの間の 1 つの出力サンプル遅延の差を排除します。HDL Cosimulationブロックがフィードバック ループ内にあり、代数ループの警告またはエラーが生成される場合は、このチェック ボックスをオフにします。データ パス上にレジスタがある順序回路をシミュレーションする場合、直接フィードスルーを指定しても、そのデータ パスのタイミングには影響しません。

Full HDL Name — 信号パス名

string

HDL シミュレーターのパス名構文を使用して信号パス名を指定します。たとえば、 manchester.samp Xcelium です。信号は、HDL デザイン階層の任意のレベルにあります。信号に対応するHDL Cosimulationブロックの端子には、この名前が付けられます。

Simulinkでのポートおよびモジュールのパス名の指定に関するルールについては、「コシミュレーション用の HDL 信号/ポートおよびモジュール パスの指定」を参照してください。

HDL シミュレーターのwaveウィンドウから信号パス名を直接コピーし、 Full HDL Nameフィールドに貼り付けることができます。Path.Nameビューではなく、 Db::Path.Nameビューを使用してください。信号パス名をFull HDL Nameに貼り付けた後、 Applyをクリックして貼り付け操作を完了し、信号リストを更新します。

依存関係

ブロックがコシミュレーション ウィザードから生成された場合、この値は変更しないでください。Vivado HDL Cosimulation ブロックの場合、パラメーターは読み取り専用です。

I/O Mode — 端子の方向

Input | Output

双方向ポートを追加するには、ポートを入力と出力の両方としてリストに 2 回追加します。

Input — HDL は、 Simulinkがドライブすることを示します。 Simulink は、指定されたサンプル レートで指定された HDL シミュレーター信号に値を配置します。

メモ

ブロックの入力端子を定義するときは、その信号への入力を駆動するソースが 1 つだけ設定されていることを確認してください。たとえば、複数のインスタンスを持つ入力ポートを定義することは避けてください。複数のソースが単一信号への入力を駆動する場合、シミュレーション モデルは予期しない結果を生成します。

Output — HDL は、 Simulinkが読み取られたことを通知します。出力信号の場合は、明示的にサンプル時間を指定する必要があります。データ型を指定することもできますが、その幅は HDL の信号の幅と一致する必要があります。データ型の指定の詳細については、 Data TypeおよびFraction Lengthパラメーターを参照してください。

Simulink値がないため、 'Z' 信号にはトライステート セマンティクスがありません。双方向信号とインターフェースするには、入力に接続し、出力ドライバーの信号と入力ドライバーの出力信号の両方を有効にします。このアプローチでは、実際のトライステート バッファーが HDL に残され、解決関数が他のトライステート バッファーとのインターフェイスを処理できます。

依存関係

ブロックがコシミュレーション ウィザードから生成された場合、この値は変更しないでください。Vivado HDL Cosimulation ブロックの場合、パラメーターは読み取り専用です。

HDL Type — HDL ポート信号の種類

Logic (既定値) | Vector

この パラメーター は読み取り専用です。

コシミュレーション ウィザードで構成された HDL ポート信号のタイプを表示します。

依存関係

このパラメーターは、ブロックがVivadoコシミュレーションで使用するために生成された場合にのみ表示されます。

HDL Dims — HDLポート信号の次元

スカラー | ベクトル

この パラメーター は読み取り専用です。

コシミュレーション ウィザードで設定された HDL ポート信号の次元を表示します。

依存関係

このパラメーターは、ブロックがVivadoコシミュレーションで使用するために生成された場合にのみ表示されます。

Sample Time — 出力ポートでのサンプルの読み取り間隔

1 (既定値) | 整数

出力ポートに適用される連続サンプル間の時間間隔。

Simulink は、ここで指定されたサンプル レートで、関連する HDL シミュレーター信号から値を読み取ります。

一般に、 Simulink はポート サンプル期間を次のように処理します。

順伝播に基づいて明示的なサンプル周期を持つ信号に入力ポートを接続すると、 Simulink はそのレートをポートに適用します。

明示的なサンプル周期を持たない信号に入力ポートを接続すると、 Simulink は、指定されたすべての入力ポートのサンプル周期の最小公倍数 (LCM) に等しいサンプル周期を割り当てます。モデル。

各出力ポートに明示的なサンプル時間を指定する必要があります。

Simulinkサンプル時間のヒットに対応する HDL 時間は、Timescalesの設定によって異なります。シミュレーションのタイムスケールを参照してください。

依存関係

このパラメーターを有効にするには、 I/O Modeを Outputに設定します。

Data Type — Simulink出力信号のデータ型

Inherit (既定値) | Fixedpoint | Double | Single | Half

データ型を自動的に決定するには、Inheritを選択します。ブロックは、継承された語長が HDL シミュレーターからクエリされた語長と一致することをチェックします。一致しない場合、 Simulink はエラー メッセージを生成します。たとえば、 Signal Specificationブロックを出力に接続すると、 Inherit は、 Signal Specificationブロックで指定されたデータ型を出力に強制します。ポート。

Simulink が出力ポートに接続されている信号のデータ型を判断できない場合、HDL シミュレータにポートのデータ型を問い合わせます。たとえば、HDL シミュレーターがサイズVHDL®データ型N STD_LOGIC_VECTORを返す場合、データ型ufixN は出力ポートに強制されます。暗黙の小数部の長さは 0 です。

オプションのFraction Lengthを使用して、明示的なデータ型を割り当てることもできます。データ型を明示的に割り当てることにより、 HDL Cosimulationブロックの出力端子に固定小数点データ型を強制できます。たとえば、8 ビット出力ポートの場合、 SignをSignedに設定し、 Fraction Lengthをに設定します。 5 は、データ型をsfix8_En5に強制します。幅を強制することはできません。幅は常に HDL シミュレーターから継承されます。

Data TypeおよびFraction Lengthプロパティは、次のタイプの HDL 信号にのみ適用されます。

VHDLや

STD_LOGICなど、任意のロジック タイプのSTD_LOGIC_VECTOR信号Verilog®

wireregシグナル

依存関係

このパラメーターを有効にするには、 I/O Modeを Outputに設定します。

Vivadoシミュレータとのコシミュレーション中、このパラメーターはSimulink Data Typeとして表示されます。

Sign — 出力データ型の符号コンポーネント

Unsigned (既定値) | Signed

明示的な出力ポートのデータ型の符号指定。

依存関係

このパラメーターを有効にするには、 I/O ModeをOutputに設定し、 Data TypeをFixedpointに設定します。

Fraction Length — 出力データ型の小数ビット数

整数

固定小数点出力信号の小数部分のサイズ (ビット単位)。たとえば、8 ビット出力ポートの場合、 SignをSignedに設定し、 Fraction Lengthをに設定します。 5 は、データ型をsfix8_En5に強制します。幅を強制することはできません。幅は常に HDL シミュレーターから継承されます。

依存関係

このパラメーターを有効にするには、 I/O ModeをOutputに設定し、 Data TypeプロパティをFixedpointに設定します。

Data TypeおよびFraction Lengthプロパティは、次のタイプの HDL 信号にのみ適用されます。

VHDLや

STD_LOGICなど、任意のロジック タイプのSTD_LOGIC_VECTOR信号Verilog

wireregシグナル

Simulink Word Length — Simulinkポートのビット幅

整数 <129 | inherit

Simulinkポートのサイズ。129 より小さい正の整数として指定します。

入力ポートの場合 — この値はinherit (読み取り専用) に設定されます。

HDL ワード長パラメーターが 128 ビットより大きい場合、 Simulinkポートの寸法は、駆動信号のデータ タイプによってコンパイル時に決定されます。以下に例を示します。

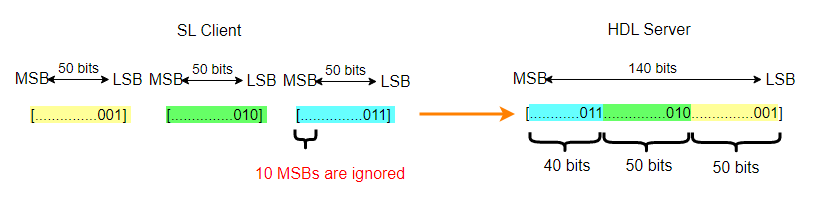

HDL ワード長 = 150 およびSimulinkワード長 = 50 の場合、 HDL Verifier™、データ幅 50 ビット、サイズ 3 のなどのSimulinkポートが許可されます。 $

sfix50(3)またはufix50(3)。HDL ワード長 = 140 およびSimulinkワード長 = 50 の場合、 HDL Verifier はSimulinkの 150 ビットを 140 ビットの HDL にパックします。 HDL Verifier は、最後のワードの 10 個の最上位ビット (MSB) を無視します。

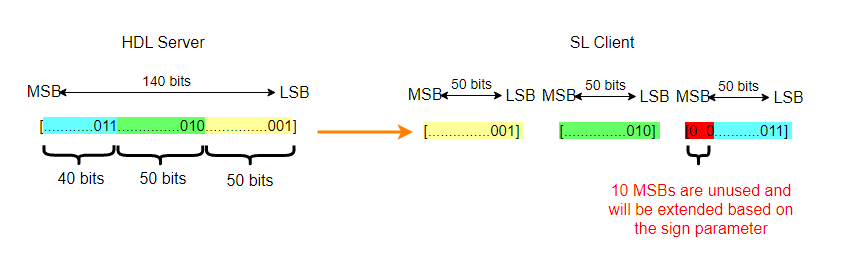

《出力ポートの場合》 — 2つのケースがあります。

HDL ワード長パラメーターが 129 ビット未満の場合、このパラメーターはHDL ポートの幅と一致し、読み取り専用になります。

HDL ワード長パラメーターが 128 ビットより大きい場合、 HDL Verifier はこのポートを表すポートのベクトルを作成します。以下に例を示します。

HDL ワード長 = 150 およびSimulinkワード長 = 50 の場合、 HDL Verifier はデータ幅 50 ビットのSimulinkポートを作成します。たとえば、

sfix50(3)やufix50(3)などです。HDL ワード長 = 150、 Simulinkワード長 = 60 の場合、 HDL Verifier は、データ幅 60 のSimulinkポート (

sfix60(3)など) を作成します。 $またはufix60(3)。HDL ワードには 150 ビットしかなく、 Simulinkポートには 180 ビットが必要なため、30 ビットが埋め込まれるか符号拡張されます。HDL ワード長 = 140 およびSimulinkワード長 = 50 の場合、HDL 出力の 50 ビットごとがSimulinkワードとして表されます。最後のSimulinkワードの MSB 10 は未使用であり、Signパラメーターに従って拡張されます。

依存関係

HDL ワード長が 129 より小さい場合、このパラメーターは読み取り専用です。

HDL Word Length — HDLポートのビット幅

整数

この パラメーター は読み取り専用です。

HDL ポートのサイズ (ビット単位)。

Verilog または SystemVerilog の例:以下のコードでは、入力In1の HDL ワード長は 140 ビット、出力Out1の HDL ワード長は 160 ビットです。

input [1:0][69:0] In1; ouput [159:0] Out1;

VHDL の例:以下のコードでは、 In1の HDL ワード長は 120 ビット、 In2 のHDL ワード長は 1200 ビットです。

TYPE matrix_of_std_logic_vector120 IS ARRAY (NATURAL RANGE <>, NATURAL RANGE <>) OF std_logic_vector(119 DOWNTO 0); In1: IN matrix_of_std_logic_vector120(0 TO 4, 0 TO 1); In2: IN std_logic_vector(1199 DOWNTO 0);

クロック

メモ

Vivadoシミュレーターとのコシミュレーション中、このタブの名前はClocks, Resets, Enablesになります。

協調シミュレーション モデルに刺激を適用するオプションの立ち上がりエッジ クロックと立ち下がりエッジ クロックを作成します。スクロール リストには、デポジット メソッドを使用して、モデル化している HDL 信号に値を駆動する HDL クロックが表示されます。クロック信号はシングルビット信号である必要があります。ベクトル信号はサポートされていません。クロック信号の追加および編集の手順については、 HDL コシミュレーション ブロックのクロック ペインを使用したオプションのクロックの作成を参照してください。

Time to run HDL simulator before cosimulation starts — 協調シミュレーションが開始されるまでの HDL シミュレーションに必要な時間

0 (既定値) | 非負の整数

コシミュレーションを開始する前に、HDL シミュレーションの実行に必要な時間を指定します。負でない整数を指定し、メニューから時間単位を選択します。

fs– フェムト秒ps– ピコ秒ns– ナノ秒us– マイクロ秒ms– ミリ秒s– 秒

依存関係

このパラメーターを有効にするには、 Vivado協調シミュレーション用にこのブロックを生成します。

Full HDL Name — 信号パス名

string

HDL シミュレーターのパス名構文を使用して、各クロックを信号パス名として指定します。例: /manchester/clkまたはmanchester.clk。

Simulinkのパス仕様の詳細と要件については、 Simulinkテストベンチ コシミュレーション用の HDL 信号/ポートおよびモジュール パスの指定を参照してください。

HDL シミュレーターのwaveウィンドウから信号パス名を直接コピーし、 Full HDL Nameフィールドに貼り付けることができます。Path.Nameビューではなく、 Db::Path.Nameビューを使用してください。信号パス名をFull HDL Nameに貼り付けた後、 Applyをクリックして貼り付け操作を完了し、信号リストを更新します。

依存関係

ブロックがコシミュレーション ウィザードから生成された場合、この値は変更しないでください。Vivado HDL Cosimulation ブロックの場合、パラメーターは読み取り専用です。

Active Clock Edge — 信号のサンプリングに使用される HDL クロック エッジ

Rising (既定値) | Falling

次のオプションのいずれかを選択します。

Rising– 立ち上がりエッジクロックを指定します。Falling– 立ち下がりエッジクロックを指定します。

期間と期間はSimulink倍です。Simulink時間を HDL 時間に関連付けるには、 [Timescales]タブに移動し、 Determine Timescale Nowをクリックします。

依存関係

このパラメーターは、 ModelSimまたはXceliumコシミュレーションでのみ表示されます。

Waveform Type — 波形を生成してクロックを駆動したり、リセットしたり、HDL 設計を有効にしたりできます。

Rising (既定値) | Falling | Step 1 to 0 | Step 0 to 1

Vivado協調シミュレーションの場合は、次のオプションのいずれかを選択します。

Active Rising Edge Clock– Simulinkが入力を駆動するときから立ち上がりエッジがオフセットされる、デューティ サイクル 50% の周期信号を作成します。Active Falling Edge Clock– Simulinkが入力を駆動するときの立ち下がりエッジがオフセットされる、デューティ サイクル 50% の周期信号を作成します。Step 0 to 1– 指定された期間だけ 0 を駆動することで開始し、その後 1 に遷移するステップ関数を作成します。Step 1 to 0– 指定された期間にわたって 1 を駆動することで開始し、その後 0 に遷移するステップ関数を作成します。

期間と期間はSimulink倍です。Simulink時間を HDL 時間に関連付けるには、 [Timescales]タブに移動し、 Show Times and Suggest Timescaleをクリックします。

依存関係

このパラメーターは、 Vivadoコシミュレーションの場合にのみ表示されます。

Period/Duration — クロック周期

2 (既定値) | 整数

明示的にクロック周期を指定するには、2 分解能単位 (ティック) 以上のサンプル時間を入力します。

クロック周期が偶数の整数でない場合、 Simulink は50% のデューティ サイクルを作成できません。代わりに、 HDL Verifierソフトウェアはclockperiod/2で立ち下がりエッジを作成します (最も近い整数に切り捨てられます)。

ModelSimまたはXceliumの場合、期間と期間はSimulink時間として指定され、 Vivadoの場合は次のようになります。 HDL 時間として指定されます。

タイムスケール

Simulinkと HDL シミュレーターの間のタイミング関係を手動または自動で選択します。これらのパラメーターは、Simulink時間の 1 秒と HDL シミュレータ時間の一定量の間の対応を指定します。この HDL シミュレータ時間は、次のいずれかの方法で表現できます。

相対 タイミング関係 (Simulink秒は、HDL シミュレータの精度、つまり「ティック」に対応します。

絶対 タイミング関係 (Simulink秒は、HDL シミュレータ時間の絶対単位に対応します)

相対タイミング モードと絶対タイミング モードの計算の詳細については、 「Simulinkと HDL シミュレータのタイミング関係の定義」を参照してください。

コシミュレーション中のSimulinkと HDL シミュレータの関係、および相対タイミング モードと絶対タイミング モードの動作の詳細については、 シミュレーションのタイムスケールを参照してください。

すべてのポート、クロック、リセット、イネーブルのSimulink時間と HDL 時間の関係を確認するには、 Show Times and Suggest Timescaleをクリックします。このアクション、必要に応じて使用可能なタイムスケールも自動的に決定されます。

Automatically determine timescale at start of simulation — 自動タイムスケールを計算するタイミング

true (既定値) | false

このオプションを選択すると、 HDL Verifier は、 Simulinkシミュレーションを開始するときにタイムスケールを計算します。このオプションが選択されていない場合は、 Determine Timescale Nowをクリックすると、シミュレーションを開始せずにタイムスケールがすぐに計算されます。Vivado協調シミュレーションの場合、このボタンはShow Times and Suggest Timescaleとして表示されます。あるいは、タイムスケールを手動で選択することもできます。自動タイムスケール計算のガイダンスについては、 タイミング関係を自動的に指定を参照してください。

1 second in Simulink corresponds to {} in the HDL simulator — Simulinkと HDL シミュレーターのタイミング関係

整数と時間の単位

このパラメーターは、 Time値とTimeUnit値で構成されます。

コシミュレーションの相対タイミング モードを設定するには、次の手順を実行します。

Tickのデフォルト設定であるTimeUnitが選択されていることを確認します。そうでない場合は、右側のリストから選択します。左側のTimeテキスト ボックスにスケール係数を入力します。デフォルトのスケール係数は 1 です。

コシミュレーションの絶対タイミング モードを設定するには、次の手順を実行します。

TimeUnit を絶対時間の単位に設定します:

fs(フェムト秒)、ps(ピコ秒)、ns(ナノ秒)、us(マイクロ秒)、ms(ミリ秒)、またはs(秒)。左側のTimeテキスト ボックスにスケール係数を入力します。デフォルトのスケール係数は 1 です。

接続

このタブは、 Vivadoシミュレータとのコシミュレーション中は表示されません。

Connection mode — SimulinkとHDLシミュレーター間の接続

Full Simulation (既定値) | Confirm Interface Only | No Connection

Simulinkと HDL シミュレーター間の接続のタイプ。

Full Simulation:インターフェイスを確認し、HDL シミュレーションを実行します。Confirm Interface Only:HDL シミュレーターに接続し、信号名、次元、データ型を確認します。ただし、HDL シミュレーションは実行しません。Simulinkシミュレーション中は、HDL シミュレーターとの接触はありません。No Connection:HDL シミュレータと通信しないでください。HDL シミュレータを起動する必要はありません。

HDL simulator is running on this computer — HDL シミュレータとSimulinkは同じホスト

true (既定値) | false

両方のアプリケーションが同じコンピュータ上で実行される場合、アプリケーション間の通信チャネルとして共有メモリまたは TCP ソケットを選択できます。このオプションを選択しない場合、TCP/IP ソケット モードのみが使用可能になり、 Connection methodリストは使用できなくなります。

Connection method — HDL シミュレータとSimulink間の接続

Socket (既定値) | Shared memory

Socket: Simulinkと HDL シミュレーターは、指定された TCP/IP ソケットを介して通信します。TCP/IP ソケット モードはより多用途です。単一システム構成およびネットワーク構成に使用できます。このオプションは最大のスケーラビリティを提供します。TCP/IP ソケット通信の詳細については、 TCP/IPソケットポートを参照してください。Shared memory: Simulinkと HDL シミュレータは共有メモリを介して通信します。共有メモリ通信は最適なパフォーマンスを提供し、デフォルトの通信モードです。

依存関係

このパラメーターは、 HDL Simulator is running on this computerを選択した場合に表示されます。

Host name — HDLシミュレータホストマシン

string

このパラメーターは、 Simulinkと HDL シミュレーターを別のコンピューターで実行する場合に適用されます。

Port number or service — ソケットのポート番号

string

共有メモリを使用していない場合は、コンピュータ システムの有効な TCP ソケット ポート番号またはサービスを指定します。TCP ソケット ポートの選択の詳細については、 TCP/IPソケットポートを参照してください。

Show connection info on icon — ブロックアイコンに接続パラメーターを追加

true (既定値) | false

このオプションを選択すると、 HDL Cosimulationブロック アイコンに現在の通信パラメーター設定が表示されます。共有メモリを選択すると、アイコンにはSharedMemが表示されます。TCP ソケット通信を選択した場合、アイコンにはSocketが表示され、ホスト名とポート番号がhostname:portの形式で表示されます。

この情報は、各ブロックが HDL シミュレーターの異なるインスタンスと通信している複数のHDL Cosimulationブロックを区別するのに役立ちます。

シミュレーション

このタブは、 Vivadoシミュレータとのコシミュレーション中は表示されません。

Time to run HDL simulator before cosimulation starts — Simulinkを HDL シミュレータと揃えるオフセット

整数と時間単位

Simulinkでシミュレーションを開始する前に HDL シミュレーターを実行する時間を指定します。この時間を指定すると、 Simulinkブロックの信号と HDL 信号が適切に調整されるため、遅延を追加することなく直接比較および検証できるようになります。

この設定は、 PreRunTime値とPreRunTimeUnit値で構成されます。

PreRunTime:任意の有効な時間値。既定値は 0 です。

PreRunTimeUnit:PreRunTimeの時間単位を指定します。

Ticksmsusnspsfs

Pre-simulation Tcl commands — コシミュレーションの前に HDL シミュレータで実行するコマンド

string

コシミュレーション ツールは、 Simulinkモデルの HDL コンポーネントをシミュレーションする前に、HDL シミュレーターでこれらのコマンドを実行します。1 行に複数のコマンドを入力する場合は、各コマンドに標準の Tcl 連結演算子であるセミコロン (;) を追加します。

たとえば、このパラメーターを使用して、シミュレーションが実行中であることを確認する 1 行の echo コマンドや、広範なシミュレーションの初期化と起動シーケンスを実行する複雑なスクリプトを生成します。これらのコマンドを使用してシミュレーション状態を変更することはできません。

任意の有効な Tcl コマンドを指定できます。指定する Tcl コマンドには、HDL シミュレータ プロジェクトをロードしたり、シミュレータの状態を変更したりするコマンドを含めることはできません。たとえば、文字ベクトルには start、 stop、またはrestart ( ModelSimの場合) などのコマンドを含めることはできません。 $$) またはrun、 stop、またはreset ( Xceliumの場合)。

Post-simulation Tcl commands — コシミュレーション後に HDL シミュレータで実行するコマンド

string

コシミュレーション ツールは、 Simulinkモデルの HDL コンポーネントをシミュレートした後、HDL シミュレーターでこれらのコマンドを実行します。

任意の有効な Tcl コマンドを指定できます。指定する Tcl コマンドには、HDL シミュレータ プロジェクトをロードしたり、シミュレータの状態を変更したりするコマンドを含めることはできません。たとえば、文字列には start、 stop、またはrestart ( ModelSim$ の場合) などのコマンドを含めることはできません。 $) またはrun、 stop、またはreset ( Xceliumの場合)。

メモ

各ModelSimシミュレーションの後、シミュレーターはカバレッジ結果を更新するのに時間がかかります。このプロセスと次の協調シミュレーション セッション間の潜在的な競合を防ぐために、連続する各シミュレーションの間に短い一時停止を追加します。

拡張機能

HDL コード生成

HDL Coder™ を使用して FPGA 設計および ASIC 設計のための VHDL、Verilog および SystemVerilog のコードを生成します。

HDL Coder には、HDL の実装および合成されたロジックに影響する追加の構成オプションがあります。Mentor Graphics® ModelSim、 Cadence® Xcelium、またはTGで使用されるコシミュレーション ブロックの HDL コードを生成できます。 Xilinx® Vivadoシミュレーター。

各HDL Cosimulationブロックは、HDL シミュレーターの下で実行される HDL モデルに入力信号を適用したり、HDL モデルから出力信号を読み取ったりすることにより、ハードウェア コンポーネントを協調シミュレーションします。コシミュレーション モデルの生成 (HDL Coder)を参照してください。

HDL コシミュレーションを設定する際のタイミング、レイテンシー、データ型指定、フレームベースの処理、およびその他の問題については、 HDL コシミュレーション ブロック インターフェイスの定義を参照してください。

HDL CosimulationブロックとHDL Coderを使用して、手動で記述した HDL コードまたは従来の HDL コードへのインターフェイスを生成できます。HDL Cosimulationブロックがモデルに含まれている場合、コーダーは選択したターゲット言語に応じてVHDLまたはVerilogインターフェイスを生成します。

ターゲット言語がVHDLの場合、生成されるインターフェースには次のものが含まれます。

エンティティ定義。エンティティは、HDL Cosimulationブロックで構成されたポートに名前とデータ型で対応するポート (入力、出力、およびクロック) を定義します。クロック イネーブル ポートとリセット ポートも宣言されます。

コンポーネント宣言、 HDL Cosimulationポートに接続された信号に対応する信号を宣言するコンポーネント構成、およびコンポーネントのインスタンス化を含む RTL アーキテクチャ。

モデルで必要なポート割り当てステートメント。

ターゲット言語がVerilogの場合、生成されるインターフェースには次のものが含まれます。

HDL Cosimulationブロックで構成されたポートに名前とデータ型が対応するポート (入力、出力、およびクロック) を定義するモジュール。このモジュールは、クロック イネーブル ポートとリセット ポート、および HDL Cosimulationポートに接続された信号に対応する

wire宣言も定義します。モジュールインスタンス。

モデルで必要なポート割り当てステートメント。

コード生成を開始する前に、モデルがコード生成の要件を満たしていることを確認してください。コード生成の要件を確認するには、 「Debug」タブを選択し、 「Update Model」をクリックします。

このブロックには 1 つの既定の HDL アーキテクチャがあります。

実装パラメーターの説明については、 ブラック ボックスまたは HDL コシミュレーション インターフェイスのカスタマイズ (HDL Coder)を参照してください。

バージョン履歴

R2008a で導入

MATLAB コマンド

次の MATLAB コマンドに対応するリンクがクリックされました。

コマンドを MATLAB コマンド ウィンドウに入力して実行してください。Web ブラウザーは MATLAB コマンドをサポートしていません。

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list:

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)