このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

HDL Verifier 入門

HDL Verifier™と、 FPGA、ASIC、および SoC のVHDL®およびVerilog®デザインをテストおよび検証できます。MATLAB® Simulink®またはTGとのコシミュレーションを使用して、 Siemens®またはQuesta®で実行されるテストベンチで RTL を検証できます。 ModelSim®、 Cadence® Xcelium™、およびXilinx® Vivado®シミュレータ。これらの同じテストベンチを FPGA 開発ボードで再利用して、ハードウェア実装を検証できます。

HDL Verifier は、 RTL テストベンチおよび完全な Universal Verification Methodology (UVM) 環境用の SystemVerilog 検証モデルを生成します。これらのモデルは、 Questa、 Xcelium、およびVivadoシミュレータ、およびSynopsys®シミュレータでネイティブに実行されます。 SystemVerilog ダイレクト プログラミング インターフェイス (DPI) 経由の VCS。

HDL Verifier は、 Xilinx、 Intel®、およびMATLABのマイクロチップ ボードの実装をデバッグおよびテストするためのツールを提供します。 。プローブをデザインに挿入し、トリガー条件を設定して内部信号をMATLABにアップロードして、視覚化と分析を行うことができます。

チュートリアル

- Verify HDL Module with MATLAB Test Bench

This tutorial guides you through the basic steps to set up an HDL Verifier™ application that uses MATLAB® to verify a simple HDL design. In this tutorial, you develop, simulate, and verify a model of a pseudorandom number generator based on the Fibonacci sequence. The model is coded in VHDL®. - Simulinkテストベンチで HDL モジュールを検証する

HDL Verifierを使用するSimulink セッションをセットアップして、単純なVHDLモデルを検証します。 - MATLAB System Object の協調シミュレーション ウィザード

Cosimulation Wizard を使用してHDL Verifier™アプリケーションをセットアップします。 - Simulinkを使用したレイズド コサイン フィルター設計の検証

コシミュレーション ウィザードを使用して、コシミュレーション用のSimulinkモデルを作成する手順を説明します。 - TLM ジェネレーターを使ってみる

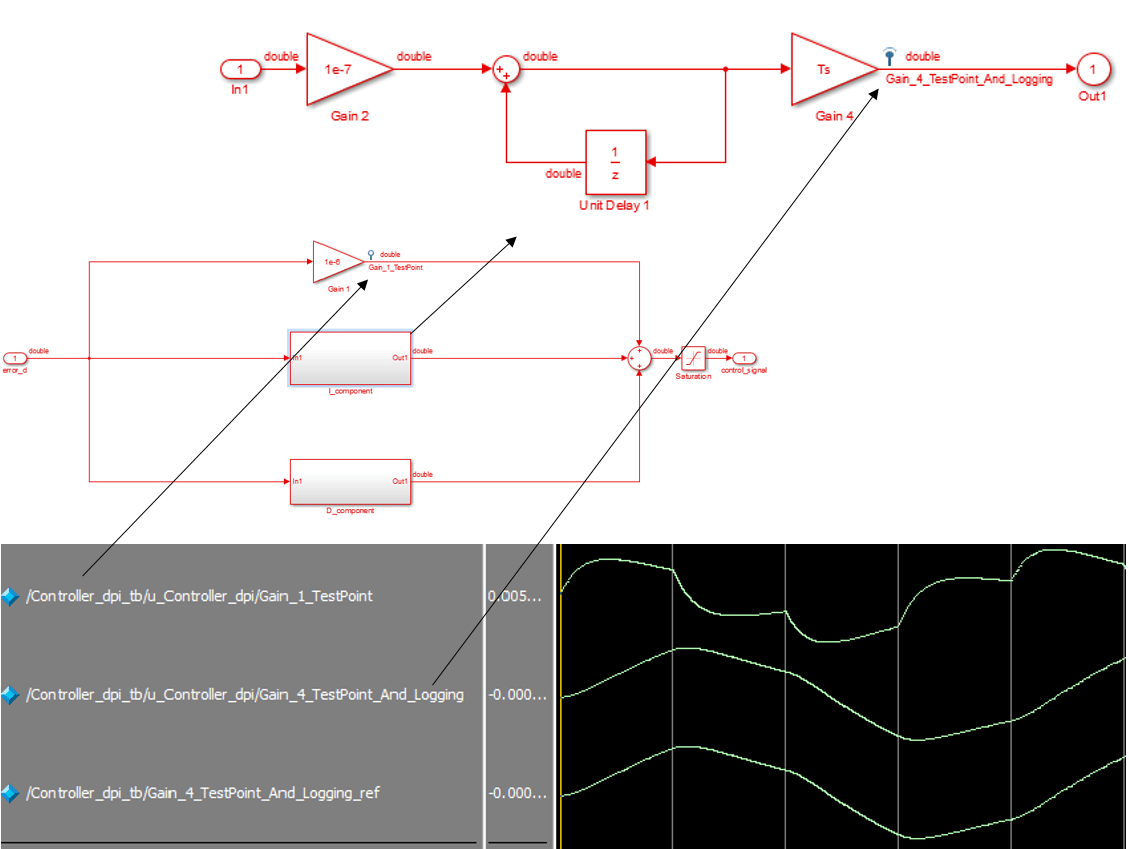

この例では、 Simulink Coder™ またはEmbedded Coder®の tlmgenerator ターゲットを使用して SystemC™/TLM コンポーネントを生成するようにSimulink®モデルを構成する方法を示します。 - Verify HDL Implementation of PID Controller Using FPGA-in-the-Loop

This example shows you how to set up an FPGA-in-the-Loop (FIL) application using HDL Verifier™. - FPGA インザループを使用したデジタル アップコンバータの検証

この例では、FPGA インザループ シミュレーションを使用して、 Filter Design HDL Coder™で生成されたデジタル アップコンバーター デザインを検証する方法を示します。 - 生成された HDL コードのテスト ベンチの選択 (HDL Coder)

生成されたテスト ベンチを選択します。 - HDL ワークフロー アドバイザーを使用したテスト ベンチの生成とコード カバレッジの有効化 (HDL Coder)

HDL ワークフロー アドバイザーを使用して生成された HDL コード用にテスト ベンチとコード カバレッジを生成します。

HDL コシミュレーション

HDLコードのインポート

TLM コンポーネントの生成

FPGA インザループ (FIL)

HDL ワークフロー アドバイザーを使用して生成された HDL コードを検証する ( HDL Coderライセンスが必要)

設計検証の自動化

- HDL コシミュレーション

HDL Verifierソフトウェアは、 MATLAB関数、 MATLAB System object™、およびのライブラリで構成されています。

- FPGAの検証

HDL Verifier は、 SimulinkまたはMATLABおよびHDL Coder™およびサポートされている FPGA 開発環境と連動して、自動的に準備を整えます。

- TLM コンポーネントの生成

HDL Verifierと、商用仮想プラットフォームを含む、OSCI 互換の TLM 2.0 環境で実行できる SystemC トランザクション レベル モデル (TLM) を作成できます。

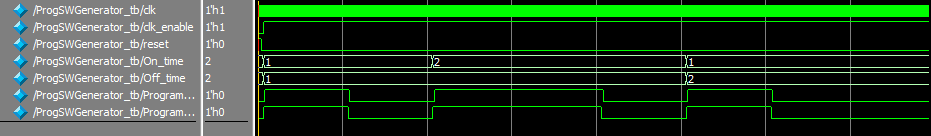

- SystemVerilog DPI コンポーネントの生成

HDL Verifier は、 Simulink Coder™またはMATLAB Coderと連携してエクスポートします。ダイレクト プログラミング インターフェイス (DPI) を備えた SystemVerilog コンポーネント内で生成された C コードとしてのサブシステム。

注目の例

ビデオ

HDL Verifier の概要

VerilogおよびVHDLの FPGA、ASIC、SoC デザインをHDL Verifierでテストおよび検証します。HDL シミュレータとのコシミュレーションを使用して、 MATLABまたはSimulinkで実行されるテストベンチで RTL を検証します。これらの同じテストベンチを FPGA および SoC 開発ボードで使用して、ハードウェアでの HDL 実装を検証します。