このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FPGA データの取得

FPGA での設計の実行中に、FPGA データ取得を使って設計からの信号を観察します。この機能は、FPGA から信号データのウィンドウを取得し、データを MATLAB® または Simulink® に返します。信号を取得するために、HDL Verifier™ は、HDL プロジェクトに統合し、残りの設計とともに FPGA に展開しなければならない IP コアを生成します。HDL Verifier は、FPGA と通信し、データを MATLAB または Simulink に返すアプリ、System object™、および Simulink モデルも生成します。

FPGA データを取得するには、次の手順に従います。

カスタマイズされたコンポーネントと IP コアを生成します。生成された IP のポート名とサイズを指定します。これらのポートは、キャプチャする信号、およびキャプチャの発生時期を制御するトリガーとして使用する信号に接続します。

生成された IP を FPGA デザインに統合し、そのデザインを FPGA ボードに展開します。HDL ワークフロー アドバイザーを使用すると、この手順は自動化されます。

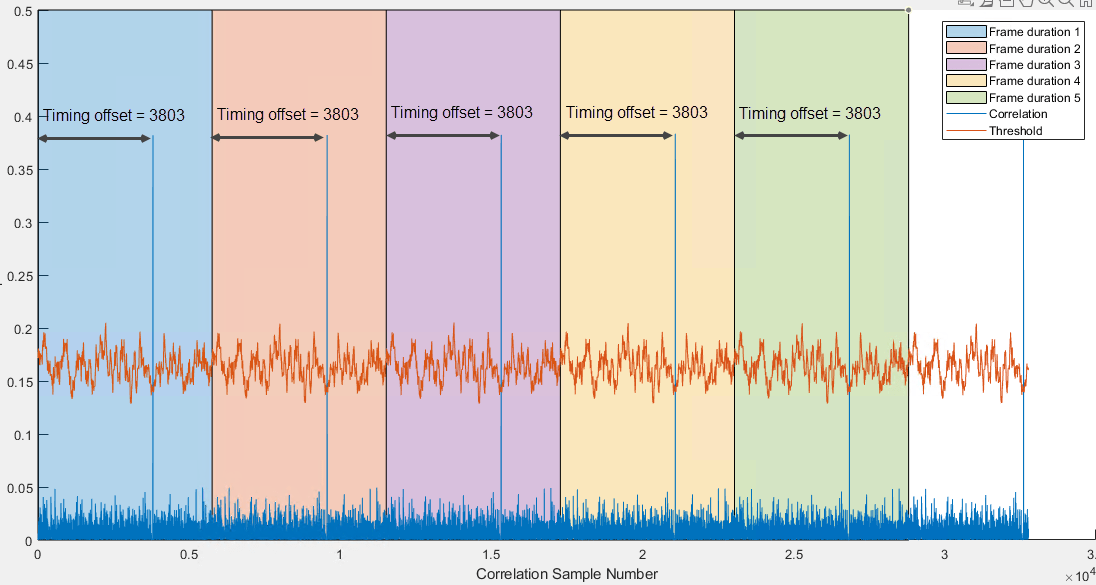

生成されたアプリ、System object、または Simulink モデルを使用して、解析、検証、または表示のためのデータを取得します。キャプチャをいつ実行するかを制御するトリガー条件と、どのデータをキャプチャするかを制御するキャプチャ条件を構成できます。

この機能を使用するには、FPGA ボード用のハードウェア サポート パッケージをダウンロードする必要があります。サポート パッケージについてはドキュメントを参照してください。Intel® FPGA ボードについては、 FPGA データの取得を参照してください。Xilinx® FPGA ボードについては、 FPGA データの取得を参照してください。

サポート パッケージのダウンロードについては、 「FPGAボードサポートパッケージをダウンロード」を参照してください。

トピック

概要

- データキャプチャのワークフロー

FPGA 上で実行されているデザインから信号データをキャプチャするための高レベルの手順。

データキャプチャの要件と準備

- FPGAボードサポートパッケージをダウンロード

FPGA ボード サポート パッケージには、FPGA インザループ (FIL) シミュレーション、FPGA データ キャプチャ、または AXI マネージャー用にサポートされているすべてのボードの定義ファイルが含まれています。 - FPGA 設計ソフトウェア ツールのセットアップ

MATLABパスをXilinx、Microchip、およびIntelソフトウェアに設定します。 - ガイド付きハードウェアセットアップ

FPGA インザループ、AXI マネージャー、または FPGA データ キャプチャで使用するハードウェアをコンフィギュレーションするための自動サポート パッケージ セットアップ プロセスの手順について説明します。 - ロジック アナライザーの構成

ロジック アナライザーで設定を調整します。