このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

ストリーミング: 面積の最適化

この例では、HDL Coder™ でサブシステム レベルのストリーミング最適化を使用する方法を示します。

はじめに

ストリーミングは、面積効率の高いハードウェアを実装するために HDL Coder でサポートされているサブシステム全体の最適化です。既定では、Simulink® モデルに対してビット アキュレートでサイクル アキュレートなハードウェアが実装されます。これは、Simulink のベクトルのデータパスがハードウェアに効率的にマッピングされないことを意味します。2 つの 64 要素のベクトル入力に対して演算を行い、64 要素のベクトル出力を生成する、Simulink の Product ブロックについて考えてみます。このブロックは、Simulink の単一のタイム ステップで乗算を 64 回実行します。サイクル アキュレートを維持するために、HDL Coder は、このブロックを生成された HDL コードで 64 個の並列な乗算器にマッピングします。FPGA で乗算器の計算量が多いとすると、これは非効率なハードウェア実装になります。

ストリーミングは、ベクトルのデータパスをスカラーまたはよりサイズが小さいベクトルのデータパスにフラット化する最適化です。並列のハードウェアの実行を直列化することにより、リソースを共有し、共有リソース全体でベクトル データを時間多重化できるようにすることを想定したものです。

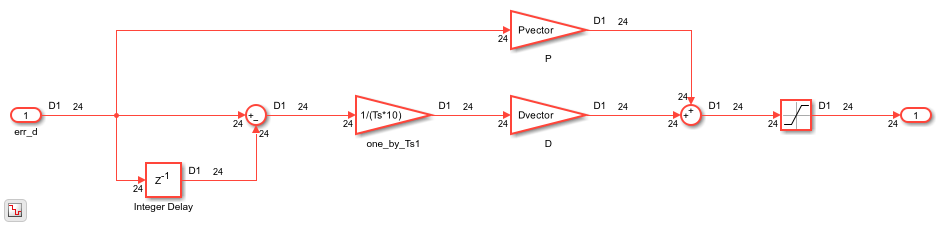

24 要素のベクトルのデータパスに対して演算を行う次のモデル例について考えてみます。このモデルには 3 つのベクトルのゲインと 2 つのベクトルの加算があり、ハードウェア実装には 72 個の乗算器と 24 個の加算器が含まれることになります。これは、HDL コードの生成時にリソース利用レポートを生成することで確認できます。

load_system('hdl_areaopt1'); open_system('hdl_areaopt1/Controller'); hdlset_param('hdl_areaopt1/Controller', 'StreamingFactor', 0); hdlset_param('hdl_areaopt1', 'ResourceReport', 'on'); makehdl('hdl_areaopt1/Controller');

### Generating HDL for 'hdl_areaopt1/Controller'.

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdl_areaopt1', { 'HDL Code Generation' } )">hdl_areaopt1</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdl_areaopt1'.

### Begin compilation of the model 'hdl_areaopt1'...

### Working on the model 'hdl_areaopt1'...

### Working on... <a href="matlab:configset.internal.open('hdl_areaopt1', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdl_areaopt1' ....

### Copying DUT to the generated model....

### Model generation complete.

### Begin VHDL Code Generation for 'hdl_areaopt1'.

### Working on hdl_areaopt1/Controller as hdlsrc/hdl_areaopt1/Controller.vhd.

### Generating package file hdlsrc/hdl_areaopt1/Controller_pkg.vhd.

### Code Generation for 'hdl_areaopt1' completed.

### Generating HTML files for code generation report at <a href="matlab:web('/tmp/Bdoc23b_2355056_2710956/tpfc16821f/hdlcoder-ex46027221/hdlsrc/hdl_areaopt1/html/hdl_areaopt1_codegen_rpt.html')">hdl_areaopt1_codegen_rpt.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc23b_2355056_2710956/tpfc16821f/hdlcoder-ex46027221/hdlsrc/hdl_areaopt1/Controller_report.html

### HDL check for 'hdl_areaopt1' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

ストリーミングによるデータパスのスカラー化

同じモデルの面積効率の高い実装を実現するには、サブシステムの StreamingFactor 実装パラメーターに正の整数値を設定します。このパラメーターは、データパスをどの程度までスカラー化するかを指定するもので、値が大きいほど面積の削減が大きくなります。この例では、24 要素のベクトルのデータパスを完全にスカラー化するために、StreamingFactor の値を 24 に指定します。これは、HDL ブロック プロパティ ダイアログ (Controller サブシステムを右クリックして開く) またはコマンド hdlset_param を使用して実行できます。

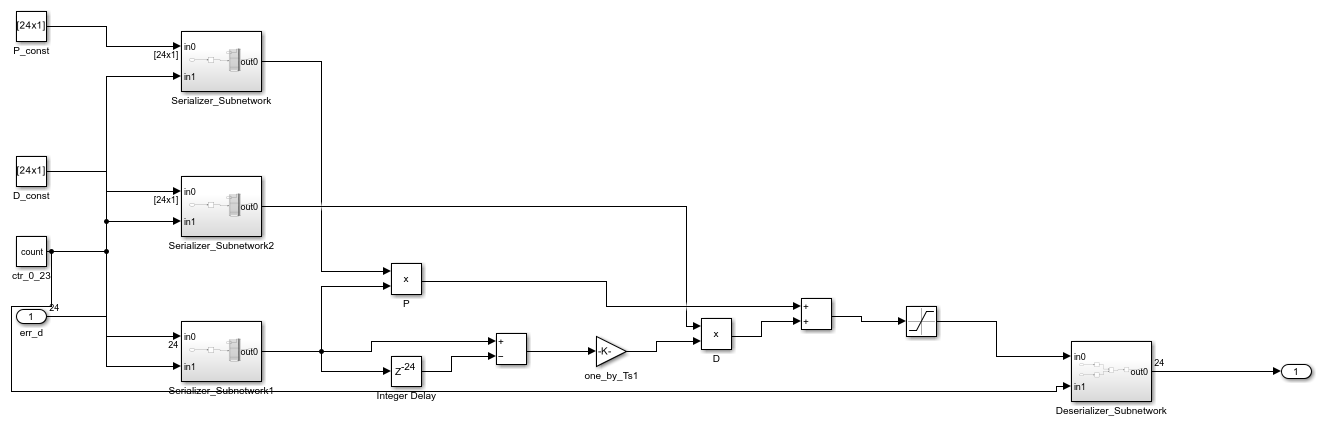

StreamingFactor を 24 に設定して HDL コードを生成すると、3 つの乗算器と 2 つの加算器だけを使用する HDL が生成されます (HDL コード生成後のリソース レポートを参照)。ストリーミングされたアーキテクチャは、ストリーミングされるサブシステムのコンテキストに応じて、局所的なマルチレートとして実装されるか、シングルレート モードで実装されます。サブシステムのロジックが遅いサンプル レートで動作している場合、またはが 1 よりも大きい値に設定されている場合は、クロックレート パイプラインが適用され、ストリーミングされたサブシステムがマルチサイクルのシングルレート アーキテクチャとして実装されます。詳細については、シングルレートのリソース共有アーキテクチャを参照してください。それ以外の場合はいずれも、この例で示すように局所的なマルチレートの実装が作成されます。ベクトルのデータパスの要素が速いレートでストリーミングされ (この例では 24 倍の速さ、赤の部分)、すべての計算がスカラーのデータパスで実行されます。出力では、デシリアライザーを使用してベクトルが再構成され、遅いレートで出力がサンプリングされます (生成されたコードの緑の部分)。

hdlset_param('hdl_areaopt1/Controller', 'StreamingFactor', 24); hdlset_param('hdl_areaopt1', 'GenerateValidationModel', 'on'); makehdl('hdl_areaopt1/Controller'); open_system('gm_hdl_areaopt1/Controller'); %set_param('gm_hdl_areaopt1', 'SimulationCommand', 'update');

### Generating HDL for 'hdl_areaopt1/Controller'.

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdl_areaopt1', { 'HDL Code Generation' } )">hdl_areaopt1</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdl_areaopt1'.

### Begin compilation of the model 'hdl_areaopt1'...

### Working on the model 'hdl_areaopt1'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdl_areaopt1', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdl_areaopt1' ....

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generating new validation model: <a href="matlab:open_system('hdlsrc/hdl_areaopt1/gm_hdl_areaopt1_vnl')">gm_hdl_areaopt1_vnl</a>.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdl_areaopt1'.

### MESSAGE: The design requires 24 times faster clock with respect to the base rate = 2.

### Begin VHDL Code Generation for 'Controller_tc'.

### Working on Controller_tc as hdlsrc/hdl_areaopt1/Controller_tc.vhd.

### Code Generation for 'Controller_tc' completed.

### Working on hdl_areaopt1/Controller as hdlsrc/hdl_areaopt1/Controller.vhd.

### Generating package file hdlsrc/hdl_areaopt1/Controller_pkg.vhd.

### Code Generation for 'hdl_areaopt1' completed.

### Generating HTML files for code generation report at <a href="matlab:web('/tmp/Bdoc23b_2355056_2710956/tpfc16821f/hdlcoder-ex46027221/hdlsrc/hdl_areaopt1/html/hdl_areaopt1_codegen_rpt.html')">hdl_areaopt1_codegen_rpt.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc23b_2355056_2710956/tpfc16821f/hdlcoder-ex46027221/hdlsrc/hdl_areaopt1/Controller_report.html

### HDL check for 'hdl_areaopt1' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

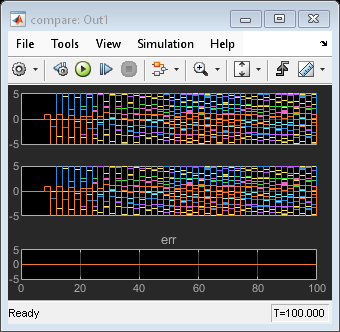

遅延の均衡化と機能的等価性

ストリーミング アーキテクチャの時間多重化を実装するレート変換によって、追加のレイテンシのサイクルが導入されます。機能的な忠実度を維持するには、このパスをメンバーとするすべてのカットセットで、この遅延を均衡化しなければなりません。ストリーミングのオプションをオンにすると、遅延の均衡化のオプション (BalanceDelays) も自動的にオンになり、この追加の遅延が自動的に均衡化されます。また、検証モデルの生成のオプションも自動的にオンになり、ユーザーは元のモデルとの機能的等価性が維持されていることを検証できます。

sim('gm_hdl_areaopt1_vnl'); open_system('gm_hdl_areaopt1_vnl/Compare/Assert_Out1/compare: Out1')

柔軟性を高めるパラメーターの使用

StreamingFactor パラメーターを調整することにより、データパスのサイズの次元に沿って設計空間を調査できます。値 1 はストリーミングなし (完全に並列な実装) を意味し、値 24 (ベクトルの全長) は最大のストリーミング (完全に直列な実装) を意味します。これらの 2 つの極値の間の値を選択して、完全に並列な実装から完全に直列な実装までの設計空間を調べることができます。

このモデル例で StreamingFactor を 6 に設定すると、生成された HDL では 4 要素のベクトルのデータパスが得られます。その結果、リソース レポートに示されるように、12 個の乗算器と 8 個の加算器が使用されます。

hdlset_param('hdl_areaopt1/Controller', 'StreamingFactor', 6); makehdl('hdl_areaopt1/Controller'); open_system('gm_hdl_areaopt1/Controller'); %set_param('gm_hdl_areaopt1', 'SimulationCommand', 'update');

### Generating HDL for 'hdl_areaopt1/Controller'.

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdl_areaopt1', { 'HDL Code Generation' } )">hdl_areaopt1</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdl_areaopt1'.

### Begin compilation of the model 'hdl_areaopt1'...

### Working on the model 'hdl_areaopt1'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdl_areaopt1', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdl_areaopt1' ....

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generating new validation model: <a href="matlab:open_system('hdlsrc/hdl_areaopt1/gm_hdl_areaopt1_vnl')">gm_hdl_areaopt1_vnl</a>.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdl_areaopt1'.

### MESSAGE: The design requires 6 times faster clock with respect to the base rate = 2.

### Begin VHDL Code Generation for 'Controller_tc'.

### Working on Controller_tc as hdlsrc/hdl_areaopt1/Controller_tc.vhd.

### Code Generation for 'Controller_tc' completed.

### Working on hdl_areaopt1/Controller as hdlsrc/hdl_areaopt1/Controller.vhd.

### Generating package file hdlsrc/hdl_areaopt1/Controller_pkg.vhd.

### Code Generation for 'hdl_areaopt1' completed.

### Generating HTML files for code generation report at <a href="matlab:web('/tmp/Bdoc23b_2355056_2710956/tpfc16821f/hdlcoder-ex46027221/hdlsrc/hdl_areaopt1/html/hdl_areaopt1_codegen_rpt.html')">hdl_areaopt1_codegen_rpt.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc23b_2355056_2710956/tpfc16821f/hdlcoder-ex46027221/hdlsrc/hdl_areaopt1/Controller_report.html

### HDL check for 'hdl_areaopt1' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.