このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

HDL QAM 送信機および受信機

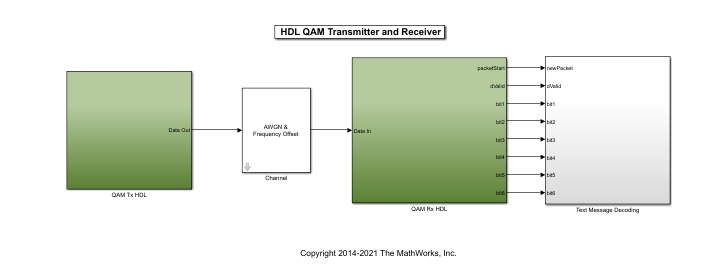

この例では、HDL コード生成をサポートする Simulink® ブロックを使用して、HDL コード生成およびハードウェア実装用に 64-QAM 送信機と受信機を実装する方法を示します。

HDL QAM Tx サブシステムは、複素数値の 64-QAM 変調コンスタレーションを生成します。受信機サブシステムの動作のデモンストレーションのため、浮動小数点チャネル モデル Channel を使用して、減衰、チャネル ノイズ、搬送波周波数オフセットおよび非整数遅延を付加します。HDL QAM Rx サブシステムは、租周波数再生、タイミング再生、フレーム同期とフレーム振幅および位相再生を使用して、チャネル劣化要因を緩和するための実用的なデジタル受信機を実装します。次に、Text Message Decoding サブシステムはデータ パケットを受信し、パケットを復号化し、それらを MATLAB® コマンド ウィンドウに出力します。

例の構造

モデルを開くには、次のように入力します。

modelname = 'commqamtxrxhdl'; open_system(modelname); set_param(modelname,'Open','on');

次のイメージは、QAM 受信機モデルの最上位構造を示したものです。QAM Tx HDL サブシステムと QAM Rx HDL サブシステムは、HDL コード生成用に最適化されています。

QAM Tx HDL サブシステムを開くには、次のように入力します。

set_param(modelname,'Open','off'); set_param([modelname '/QAM Tx HDL'],'Open','on');

次のイメージは、QAM Tx HDL サブシステムの詳細な構造を示したものです。

QAM Tx HDL サブシステムには次のコンポーネントが含まれています。これらについては、「HDL QAM 送信機」のセクションで詳しく説明されています。

Data Generation & Packetization - シンボルにマップするビットをグループ化し、送信するパケットを生成

Symbol Mapping - Data Generation & Packetization サブシステムからのビット出力を QAM シンボルにマップ

Pulse Shaping - 送信前に内挿 RRC (ルート レイズド コサイン) フィルターを使用してシンボルのパルス整形とアップサンプリングを実行

set_param([modelname '/QAM Tx HDL'],'Open','off'); set_param([modelname '/Channel'],'Open','on');

Channel サブシステムの構造は、次のとおりです。Channel サブシステムは、減衰と周波数オフセットが指定されている AWGN チャネルに類似しており、ソフトウェアで実行することを意図されています。そのため、ここでは、Phase/Frequency Offset ブロックなどのような HDL コード生成でサポートされていないブロックを使用することができます。Phase/Frequency Offset ブロックは固定小数点データ型をサポートしていません。そのため、Channel サブシステムの入力での double 型への変換もサポートしていません。信号は、Channel サブシステムから出力される前に固定小数点型に戻されます。非整数遅延と AWGN が送信信号に適用され、その信号が Gain ブロックで減衰されます。

set_param([modelname '/Channel'],'Open','off'); set_param([modelname '/QAM Rx HDL'],'Open','on');

次のイメージは、QAM Rx HDL サブシステムの詳細な構造を示したものです。

QAM Rx HDL サブシステムには次のコンポーネントが含まれています。

Automatic Gain Control - 受信信号の強度を正規化します。

Coarse Frequency Offset Correction - 受信信号のおおよその周波数オフセットを推定して補正。このサブシステムには、係数 2 でダウンサンプリングする Root Raized Cosine Receive Filter ブロックも含まれます。

Timing Recovery - 再生されたタイミング ストローブに従って入力信号をリサンプルし、適切なサンプリング時点においてシンボル判定を実行します。

Magnitude & Phase Recovery - パケット検出、位相と振幅の細かな補正を実行します。

Demodulate - 信号を復調し、シンボルをビットにマッピング解除します。

set_param([modelname '/QAM Rx HDL'],'Open','off'); set_param([modelname '/Text Message Decoding'],'Open','on');

次のイメージは、Text Message Decoding サブシステムの構造を示したものです。

このサブシステムはソフトウェアで実行されるように設計されているため、サブシステムはフレームベースの信号を使用して計算を高速化します。Text Message Decoding サブシステムには、8 つのサンプルベース boolean 入力信号 (dValid、packetStart、および信号 bit1 ~ bit6) があります。dataframer MATLAB Function ブロックは、サンプルベースの信号をフレームベースの信号に変換します。復調されたビットは、dValid が高位に設定されている場合にのみ有効です。dataframer ブロックは、dValid 信号を使用して遅延線を受信ビットで満たし、newPacket 信号を使用して遅延線に格納されたデータを出力に転送し、遅延線をリセットします。

Descramble and Print サブシステムは、イネーブル信号が high になった場合にのみ受信データを処理します。以上のことは、遅延線に 336 の復調された有効ビットが蓄積された場合、または newPacket 信号が高位の場合に発生します。これにより、dataframer ブロックが RxGo 信号を高位に設定します。シミュレーションの実行中、Descramble and Print サブシステムは、文字列 "Hello world! ~64QAM test string~ ###" を MATLAB コマンド ウィンドウに出力します。ここで、'###' は '000'、'001'、'002'、...、'099' の繰り返しシーケンスです。サブシステムは、50 パケットごとに、正常に受信された直近の 50 パケットにおけるデータのビット エラー レートを MATLAB コマンド ウィンドウに出力します。

HDL QAM 送信機

HDL QAM Tx には、Data Generation & Packetization ブロック、Symbol Mapping ブロック、および Pulse Shaping ブロックが含まれます。

Data Generation & Packetization

Controller FSM および Data Source サブシステムは、プリアンブル ビットとデータ ビットを生成し、スクランブルを実行してパケットを構築します。各パケットは、84 ビットのバーカー符号プリアンブルと 252 ビットのスクランブルされたデータから構成されます。Group Bits ブロックは、シンボル マッパーの要求に応じて、入力データ ビット ストリームを入力サンプル レートの 1/6 で 6 ビット整数に変換します。

Data Source サブシステムには 2 サンプルのパイプライン遅延があります。さらに、データ ソースとビット ペアリング サブシステムの間にパイプライン遅延があります。そのため、有効な信号はデータ パスのパイプライン遅延に合うように遅延されます。Group Bits サブシステムは、サンプル レートを 6 分の 1 に減らします。有効なコントロール パスで係数 6 のダウンサンプリングを行うことにより、有効なコントロール パスのサンプル レートが信号パスのサンプル レートと一致するようになります。

set_param([modelname '/Text Message Decoding'],'Open','off'); set_param([modelname '/QAM Tx HDL/Data Generation & Packetization'],'Open','on');

Controller FSM - Controller FSM ブロックは、制御ステート マシンを実装する MATLAB Function ブロックです。FSM には 2 つの状態、Pack_Preamble と Append_Data があります。Pack_Preamble 状態は、load_preamble 信号をアサートし、reset_preamble 信号および load_data 信号をアサート解除します。FSM は 84 クロック サイクルの間、この状態を維持します。次に、FSM は load_preamble 信号をリリースすると同時に Append_Data 状態に移行し、load_data 信号と reset_preamble 信号をアサートします。FSM は 252 クロック サイクルの間、この状態を維持します。load_preamble と reset_preamble は boolean で、各パケットの開始時のプリアンブルの負荷を管理する Preamble Address Counter を制御するために使用されます。load_data 信号は boolean で、パケットへのデータの読み込みを制御する Data Address Counter を有効にします。

Data Source - Data Source サブシステムには、プリアンブルとデータ ビットを保存する 2 つのルックアップ テーブル (LUT) が含まれています。Preamble Address Counter サブシステムは、Controller FSM ブロックによって生成される reset_preamble 信号と load_preamble 信号によって制御され、preamble lookup LUT を解決します。Data Access Counter は、Controller FSM ブロックによって生成される load_data 信号によって有効にされ、data lookup LUT を解決します。Preamble Address Counter サブシステムには、Controller FSM ブロックによって生成されるリセット信号があり、各パケットの先頭に同じプリアンブルが挿入されます。データ アドレス シーケンスが非常に長くなり、各パケット内に異なるデータ ビットが配置されることでパケットごとに変化するため、Data Address Counter サブシステムにはリセット信号がありません。さらに、データ LUT のカウンターを有効にするため、load data 入力は、Preamble Data Mux ブロックによるプリアンブルまたはデータ ビットの選択を HDL Data Scrambler コンポーネントが有効にするタイミングを制御します。

set_param([modelname '/QAM Tx HDL/Data Generation & Packetization'],'Open','off'); set_param([modelname '/QAM Tx HDL/Data Generation & Packetization/Data Source'],'Open','on');

HDL Data Scrambler - HDL Data Scrambler ブロックを表示するには、次のように入力します。

set_param([modelname '/QAM Tx HDL/Data Generation & Packetization/Data Source'],'Open','off'); set_param([modelname '/QAM Tx HDL/Data Generation & Packetization/Data Source/HDL Data Scrambler'],'Open','on');

次のイメージは、HDL Data Scrambler サブシステムを示したものです。サブシステムは、XOR ゲート (剰余 2 の加算用) とレジスタを使用します。有効にされたサブシステムにより、処理すべき新しい入力データがある場合にのみスクランブラーが有効になります。

Group Bits - Group Bits サブシステムは、6 つの個別のビットを 6 ビット符号なし整数出力 (Symbol Mapping コンポーネントに必要な入力形式) にグループ化します。遅延は、Bit Concat ブロックの入力で 6 ビットを整列させるために使用され、6 ビットの符号なし出力に連結されます。その後、この出力がダウンサンプリングされて、正しくグループ化されたビットが選択されます。

set_param([modelname '/QAM Tx HDL/Data Generation & Packetization/Data Source/HDL Data Scrambler'],'Open','off'); set_param([modelname '/QAM Tx HDL/Data Generation & Packetization/Group Bits'],'Open','on');

Symbol Mapping

Symbol Mapping サブシステムは、Rectangular QAM Modulator Baseband ブロックを使用して整数入力値を対応する 64-QAM 複素数値シンボルにマップします。このブロックではグレイ マッピング方式を使用します。

set_param([modelname '/QAM Tx HDL/Data Generation & Packetization/Group Bits'],'Open','off'); set_param([modelname '/QAM Tx HDL/Symbol Mapping'],'Open','on');

Pulse Shaping

Pulse Shaping サブシステムは、アップサンプリング係数 4 の RRC Interpolation Filter ブロックを使用します。整合フィルターが受信機に実装されています。フィルターはパイプライン化されます。

set_param([modelname '/QAM Tx HDL/Symbol Mapping'],'Open','off'); set_param([modelname '/QAM Tx HDL/Pulse Shaping'],'Open','on');

HDL QAM 受信機

HDL QAM Rx には、次のブロックが含まれます。Automatic Gain Control, Coarse Frequency Offset Correction, Timing Recovery, Magnitude & Phase Recovery, and Demodulate

Automatic Gain Control

Automatic Gain Control サブシステムは、Coarse Frequency Compensation の入力の振幅が 1 ~ -1 の範囲に正規化されるようにします。

set_param([modelname '/QAM Tx HDL/Pulse Shaping'],'Open','off'); set_param([modelname '/QAM Rx HDL/Automatic Gain Control'],'Open','on');

次のイメージは、Automatic Gain Control サブシステムの構造を示したもので、モデルのパイプライン レジスタが緑色になっています。

Coarse Frequency Offset Correction

Coarse Frequency Offset Correction サブシステムは、Luise-Reggiannini アルゴリズム [1] を使用して周波数オフセットを推定し、補正します。Frequency Offset Estimation サブシステムは、Root Raised Cosine Receive Filter ブロックの出力に基づいて推定を行い、その後、その推定に基づく周波数オフセットの修正を Root Raised Cosine Receive Filter への入力で適用します。これにより、受信信号帯域幅の必要な部分と受信フィルターの周波数応答とがより一層対応し、Root Raised Cosine Receive Filter ブロックの出力での修正に比べて SNR が改善されます。

推定および補正アルゴリズムは閉ループ内での演算であり、以前の周波数オフセットの推定値を反復的に更新するため、システムは徐々に結果に向かって収束します。Loop Gain は推定値を平均します。このアーキテクチャは、[1] で説明されています。Root Raised Cosine Receive Filter ブロックがダウンサンプリング演算を実装するので、フィルターへの入力でレートが一致するようにするには、Repeat ブロックを使用してフィードバック信号をアップサンプリングする必要があります。

Coarse Frequency Offset Correction サブシステムの出力では、Coarse Frequency Offset Correction サブシステムが新しい推定を行うときにサブシステムへの入力における周波数オフセットが同じままであっても、時間の経過とともに変化する残留周波数オフセットがあるということに注意してください。Magnitude and Phase Recovery サブシステムは、残留オフセットを細かく補正します。

set_param([modelname '/QAM Rx HDL/Automatic Gain Control'],'Open','off'); set_param([modelname '/QAM Rx HDL/Coarse Frequency Offset Correction'],'Open','on');

Frequency Offset Estimation: Frequency Offset Estimation サブシステムは Luise-Regiannini アルゴリズム ([1] を参照) を実装します。サブシステムは、[2] で説明されているように、信号を 4 乗して 4 次の位相推定器を実装します。ハードウェア性能の向上のために付加されたパイプライン化とともに、カスケード接続された 2 つの Product ブロックによって、推定器が実装されます。Discrete FIR Filter は、すべてが 1 で構成される矩形重み付きフィルター ([1] を参照) を実装します。FIR Scale はフィルター ゲインを考慮して FIR 出力をスケーリングします。Complex To Magnitude-Angle HDL Optimized ブロックは、Luise-Reggiannini アルゴリズムで必要な関数 を実装するために使用されます。このブロックはハードウェア フレンドリな CORDIC アルゴリズムを使用して位相を計算します。詳細については、Complex to Magnitude-Angle (DSP HDL Toolbox)ブロックを参照してください。Frequency Offset Estimation サブシステムから出力される前に、信号は Luise-Regiannini アルゴリズムで必要な場合はスケーリングされ、さらに、NCO の語長に合うようにスケーリングされます。

set_param([modelname '/QAM Rx HDL/Coarse Frequency Offset Correction'],'Open','off'); set_param([modelname '/QAM Rx HDL/Coarse Frequency Offset Correction/Frequency Offset Estimation'],'Open','on');

Timing Recovery

Timing Recovery サブシステムを開くには、次のように入力します。

set_param([modelname '/QAM Rx HDL/Coarse Frequency Offset Correction/Frequency Offset Estimation'],'Open','off'); set_param([modelname '/QAM Rx HDL/Timing Recovery'],'Open','on');

次のイメージは、Timing Recovery サブシステムを示したものです。

Timing Recovery サブシステムは PLL ([3] の Chapter 8 を参照) を実装し、受信信号のタイミングの誤差を補正します。Timing Recovery サブシステムは平均して、入力サンプル 2 つにつき出力サンプルを 1 つ生成します。

Interpolation Control ブロックは剰余 1 の減算カウンター ([3] の Chapter 8.4.3 を参照) を実装し、Interpolation Filter の内挿の選択を容易にするための制御信号を生成します。この制御信号は Timing Error Detector (TED) も有効にし、正確なタイミングの時点でタイミング誤差を計算するようにします。Interpolation Control サブシステムは、Interpolation Filter のタイミング差 mu を更新し、最適なサンプリング時点で内挿を生成します。

Interpolation Filter は、[3] の Chapter 8.4.2 で説明されているように、 をもつ Farrow パラボリック フィルターです。このフィルターでは 0.5 の が使用されているため、すべてのフィルター係数は 1、-1/2、3/2 のいずれかになり、内挿構造は大幅に簡素化されます。Timing Error Detector は、[3] の Chapter 8.4.1 で説明されているように、内挿に基づいて、ゼロクロッシングの際にタイミング誤差を生成します。

タイミング誤差を補正するため、内挿フィルターによって信号で非整数遅延が発生するようにします。この非整数遅延は mu 入力信号によって制御します。タイミング誤差 (遅延) がシンボルの境界に達すると、出力の内挿が 1 つ超過/不足してしまいます。この内挿の超過または不足に対処するため、タイミング誤差検出器にはビット スタッフィングまたはスキッピングが実装されます。

ビット スタッフィングとスキッピングの詳細については、[3] の Chapter 8.4.4 を参照してください。タイミング再生ループは通常、入力サンプル 2 つにつき 1 出力サンプルの割合で生成します。また、入力サンプルレートで実行されるタイミング ストローブ (validOut 信号) も出力します。通常の場合、ストローブの値は 1 と 0 が交互に並んだシーケンスです。しかし、これが起きるのは送信機と受信機間の相対遅延になにかしらの 1 シンボル周期の分数部が含まれ、かつ (シンボル間の) 遅延の整数部が一定である場合のみです。相対遅延の整数部が変化すると、ストローブ値に 0 または 1 が 2 回連続で出力されてしまう場合があります。

Magnitude & Phase Recovery

Magnitude & Phase Recovery サブシステムは、パケット同期、および細かな周波数再生と振幅再生を実施します。

set_param([modelname '/QAM Rx HDL/Timing Recovery'],'Open','off'); set_param([modelname '/QAM Rx HDL/Magnitude & Phase Recovery'],'Open','on');

パケット同期: Preamble Matched Filter サブシステムは、プリアンブルの時間反転複素共役をフィルターの重みとして使用します。Preamble Matched Filter サブシステムの出力の係数は Modulus サブシステムを使用して計算されます。その後、Modulus サブシステムの出力がしきい値と比較されて、パケットの先頭のプリアンブルが検出されます。この MATLAB Function ブロックは、信号 isPreamble を生成します。この信号は各パケットのプリアンブルの間は高位に保持されます。また、MATLAB function ブロックは dvalid 信号も生成します。この信号はプリアンブルが検出されたときはパケットの存続期間中高い値に設定されます。

振幅と位相の細かな再生: 1-Tap DLMS (遅延最小平均二乗) フィルター サブシステムは、プリアンブルに適応し、Desired Signal Source によって生成される基準信号を使用するというものであり、位相誤差と振幅誤差の両方を補正します。isPreamble 信号は、MATLAB Function ブロックで生成され、パケットが検出された後、14 個のプリアンブル シンボルの期間は高位に維持されます。この信号を使用して、必要な信号ソースを有効にし、1-Tap DLMS の Adapt 入力を有効にします。isPreamble 信号が低位の場合、1-Tap DLMS の重みが保持され、Desired Signal Source がリセットされます。ここで遅延 LMS (DLMS) [4] アルゴリズムを使用することにより、より一層のパイプライン処理の導入が可能です。その結果、フィルターのクリティカル パスが減り、ハードウェアでの実装後の実現可能な最大クロック レートが高まります。

Desired Signal Source サブシステムの内部構造を次に示します。data lookup LUT にはプリアンブル シンボルが含まれています。

set_param([modelname '/QAM Rx HDL/Magnitude & Phase Recovery'],'Open','off'); set_param([modelname '/QAM Rx HDL/Magnitude & Phase Recovery/Desired Signal Source'],'Open','on');

1-Tap DLMS サブシステムの内部構造を次に示します。

set_param([modelname '/QAM Rx HDL/Magnitude & Phase Recovery/Desired Signal Source'],'Open','off'); set_param([modelname '/QAM Rx HDL/Magnitude & Phase Recovery/1-Tap DLMS'],'Open','on');

Demodulate

Demodulate サブシステムは、各 64-QAM 入力シンボルをビットにマップして、入力シンボルごとに 6 ビットを出力します。Rectangular QAM Demodulator Baseband ブロックの HDL コードを生成するため、シンボル間の最大距離は 2 に設定しなければなりません。これは、送信機で生成されるシンボル間の距離の 8 倍です。したがって、それに応じて Demodulate サブシステムへのシンボル入力がスケールアップされなければなりません。この操作は、Shift Arithmetic ブロックを使用して行います。このブロックで、バイナリ ポイントを 3 ビット分だけ左にシフトして、必要な 8 の倍数にします。

set_param([modelname '/QAM Rx HDL/Magnitude & Phase Recovery/1-Tap DLMS'],'Open','off'); set_param([modelname '/QAM Rx HDL/Demodulate'],'Open','on');

結果と表示

シミュレーション中、正常に受信されたパケットが MATLAB コマンド ウィンドウに表示されます。MATLAB コマンド ウィンドウは、50 パケットごとに、正常に受信された直近の 50 パケットにおけるデータのビット エラー レートを表示します。

シミュレーションの実行後、モデルには受信機性能のさまざまな側面を示す 6 つの異なる図が表示されます。以下にこれを示し、各プロットについて説明します。最初の 5 つのプロットは、Automatic Gain Control、Frequency Offset Estimation、Timing Recoveryの位置推定、Timing Recovery サブシステムの出力と Magnitude & Phase Recover サブシステムの出力におけるコンスタレーションの実数部について、シミュレーション期間中の適応の様子を示しています。最後のプロットは、なんらかの適応が行われた後の Magnitude & Phase Recovery サブシステムの出力におけるコンスタレーション ダイアグラムを示しています。

set_param([modelname '/QAM Rx HDL/Demodulate'],'Open','off'); print_cap = evalc('sim(modelname)'); %#ok<NASGU> clear print_cap; tscope1.hide; tscope2.hide; tscope3.hide; constDiag1.hide; constDiag2.hide; constDiag3.hide;

自動ゲイン制御のプロット

次のプロットは、出力が正規化されるまでの時間経過に伴う Automatic Gain Control サブシステムの適応の様子を示しています。自動ゲイン制御の適応までの時間と、ゲインが比較的安定したレベルに達した後のリップル数とでバランスをとらなければなりません。自動ゲイン制御ループ ゲインを大きくすると、適応にかかる時間は短くなりますが、適応後の振幅の変動が大きくなります。ループ ゲインを小さくすると、自動ゲイン制御の適応速度が遅くなり、適応後のレベルが滑らかになりますが、適応にかかる時間が長くなります。

tscope1.show;

周波数オフセット推定のプロット

次のプロットは、租周波数オフセットが、システムにより組み込まれた周波数オフセット (青い水平線で表示) に向かって徐々に適応していく様子を示しています。次のイメージは、推定値が実際の周波数オフセットに近づいているものの、まだ残留誤差があり、後にシステムにおいて解決しなければならないことを示しています。

tscope1.hide; tscope2.show;

タイミング再生位置のプロット

次のプロットは、Interpolation Filter に対する mu 入力を示しています。シミュレーション中はチャネル遅延が変化しないため、時間の経過とともに多少のリップルはあるものの、mu が定常状態に収束することに注意してください。

tscope2.hide; tscope3.show;

タイミング再生出力の実数部のプロット

次のプロットは、Timing Recovery サブシステムの出力の実数部が 64QAM で想定されている 8 つの個別の振幅レベルへと収束し始めている様子を示しています。ただし、この段階では、祖周波数再生後に残る残留周波数オフセットがまだ受信機で修正されていないので、いくつかの時点では、比較的はっきりと観測できる個々の振幅レベルにおいて、他の場所に比べて信号の品質にばらつきがあります。この時点では、まだ受信機でコンスタレーションが若干回転します。

tscope3.hide; constDiag1.show;

シンボル推定値の実数部のプロット

次のプロットは、Magnitude & Phase Recovery サブシステムの出力の実数部が時間の経過に伴って適応していく様子を示しています。上記のプロットとは異なり、この図は詳細な周波数再生の後に生成されているため、コンスタレーションは回転しません。ブロックからの出力が有効でないため最初はサンプルがなく、その後、8 つの明確な振幅レベルが示されます。これらは、64-QAM コンスタレーションの 8 つの実際の振幅レベルを表しています。

constDiag1.hide; constDiag2.show;

再生されたコンスタレーション プロット

次のプロットは、システムにおけるチャネルへの適応時間経過後の Magnitude & Phase Recovery サブシステムの出力時のコンスタレーションを示しています。チャネル ノイズが減ると各コンスタレーション点のサイズが小さくなり、チャネル ノイズが増えると個々のコンスタレーション点が収束し始めます。システムで周波数オフセットに対する修正が正常に行われなかった場合、ここでコンスタレーションの回転が観測されます。

constDiag2.hide; constDiag3.show;

参考文献

1.Luise, M., and R. Reggiannini. “Carrier Frequency Recovery in All-Digital Modems for Burst-Mode Transmissions.” IEEE Transactions on Communications 43, no. 2/3/4 (February 1995): 1169–78. https://doi.org/10.1109/26.380149.

2.Moeneclaey, M., and G. de Jonghe. “ML-Oriented NDA Carrier Synchronization for General Rotationally Symmetric Signal Constellations.” IEEE Transactions on Communications 42, no. 8 (August 1994): 2531–33. https://doi.org/10.1109/26.310611.

3.Rice, Michael.Digital Communications: A Discrete-Time Approach. Upper Saddle River, N.J: Pearson/Prentice Hall, 2009.

4.Long, G., F. Ling, and J.G. Proakis. “The LMS Algorithm with Delayed Coefficient Adaptation.” IEEE Transactions on Acoustics, Speech, and Signal Processing 37, no. 9 (September 1989): 1397–1405. https://doi.org/10.1109/29.31293..

constDiag3.hide;

close_system(modelname);

clear modelname;