ルネサスがASIC用の画像処理IPコアをモデルベース デザインにより設計および実装

「モデルベース デザインにより、私たちはアルゴリズムおよびシステムの機能を早期に検証し、仕様変更により速く適合し、従来の設計フローよりも多くの設計選択肢を評価することができます。モデルベース デザインは、アルゴリズム・エキスパートおよびRTLエンジニアの間のギャップを埋めるのを支援します。」

課題

自動車用のディスプレイおよびデジタル画像機器用の画像処理IPコアのアルゴリズムを開発すること。

ソリューション

MATLABとSimulinkによるモデルベース デザインを使用し、アルゴリズムをモデル化し、固定小数点変換し、シミュレーションによって検証し、合成可能なHDLコードを生成。

結果

- 複数の最適化、選択肢の設計案を調査

- 効率的なHDLコードを生成

- 実践的なエンジニア技能を迅速に獲得

ルネサスエレクトロニクスの設計とアプリケーション技術の会社であるルネサスシステムデザイン株式会社はエレクトロニクス製品用の中核技術およびASIC、大規模集積回路(LSI)システムおよびマイクロコンピュータを開発しています。これらの中核技術の中には、自動車用のディスプレイシステムおよびデジタル画像機器で使用される高度な画像処理およびフィルター処理アルゴリズムがあります。

ASIC向け画像処理IPコアの設計および実装を加速するために、ルネサスのエンジニアは、MATLAB®とSimulink®によるモデルベースデザインを採用しました。

「私たちが開発するIPコアは複数の製品に使用されるので、高品質でかつ柔軟でなければなりません」と神谷 衛氏(ルネサスシステムデザイン株式会社 主任技師)は述べています。「モデルベース デザインにより、開発の初期段階でリアルタイム・プロトタイプを作成し、設計の選択肢について系統的に調査し、より多くのテストケースによる広範囲なシミュレーションによって私たちの設計に自信を持つことができるようになり、これらのゴールを達成することができました。」

課題

従来のワークフローでは、ルネサスのエンジニアは、静止画像データにより、初期段階の画像処理アルゴリズムを検証しました。しかし、それがHDLで実装され、ビデオ・ストリームデータでテストされた時点で、静止画像による検証では明らかにできなかったアルゴリズムに関する問題が検出されることもありました。実際にはそのような遅い段階で必要な変更を加えることは困難で、スケジュール内に根本的な修正の実装およびテストを行うための時間は十分に無いこともありました。

また、ルネサスではアルゴリズムはまず浮動小数点のCコードで記述されていました。浮動小数点コードを固定小数点コードに変換する作業は、アルゴリズムを理解し、かつRTL(Resister Transfer Level)記述に精通していた、経験のあるごく少数のエンジニアに依存していました。この時間がかかる重要な作業が少数のエンジニアに依存している状況はプロジェクトにおいてボトルネックを生じる原因となりました。HDLコードは、固定小数点Cコードに基づいてハンドコーディングによって記述され、その結果さらなる遅れを引き起こしました。

ルネサスは、アルゴリズムのリアルタイム検証を開発初期に完了することを可能にする開発アプローチを必要としました。さらに、浮動小数点から固定小数点への変換およびHDLコードの作成に関連したボトルネックを最小化しようという試みがなされました。

ソリューション

ルネサスのエンジニアは、画像処理アルゴリズム開発および実装のためにモデルベース デザインを採用しました。

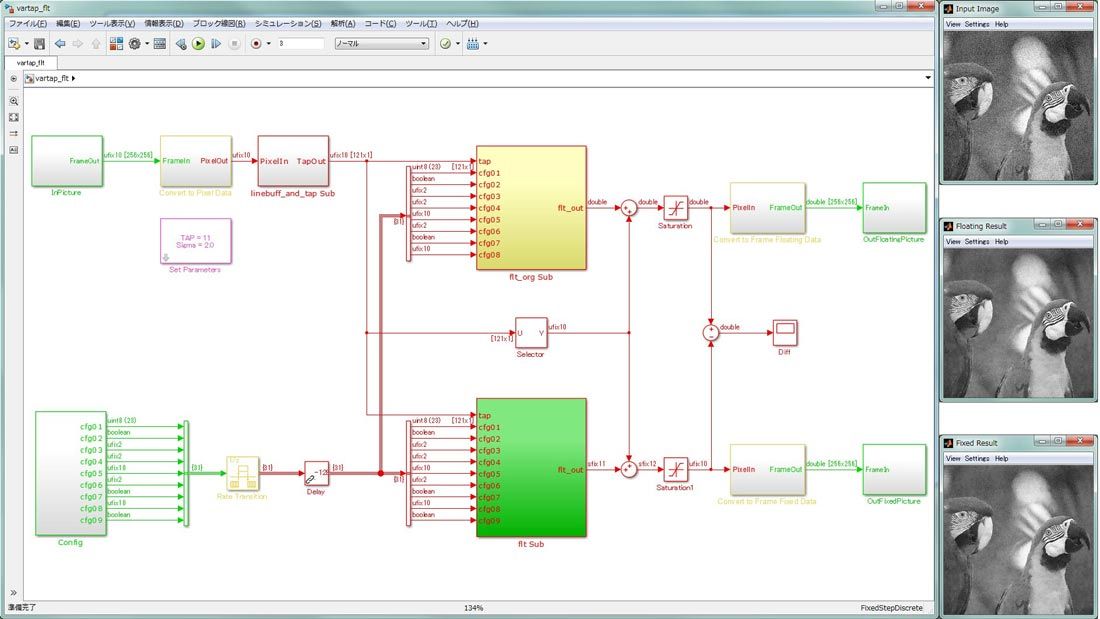

MATLABとSimulinkにより、エンジニアは、要求仕様に基づいた画像処理システムの浮動小数点モデルを開発しました。それらは、シミュレーションによって生成された出力画像の効果を視覚的に検証することで、モデルを用いた早期機能検証を実施しました。

システムモデルからの出力画像の視覚化には、Computer Vision Toolbox™が使用されました。

さらに、Fixed-Point Designer™により、浮動小数点の設計を固定小数点に変換しました。Fixed-Point Designerの固定小数点アドバイザー機能によって、オーバーフローとアンダーフローの条件を検知し、変換の手順を自動化することができました。

固定小数点と浮動小数点のシミュレーション結果を比較した後、最適化されたSimulinkモデルからの合成可能なHDLコードを生成するためにHDL Coder™が使用されました。

HDL CoderおよびHDL Verifier™の使用により、テストベンチが生成され、SimulinkおよびCadence® Incisive®による協調シミュレーションによってHDLが検証されました。次に、要求仕様を満たすよう、設計の速度と面積を最適化しました。リソース・シェアリングやパイプラインオプションなどのパラメータ設定の組み合わせを複数切り替えてHDL Coderからコード生成し、Synopsys® Design Compilerにより論理合成され、最適な設計は合成結果と仕様の比較によって選ばれました。この繰り返しによる設計プロセスを自動化するためにMATLABスクリプトを使用しました。また、その結果、手作業のプロセスと比べ、パラメータ・セッティングのより広範な選択肢から設計を最適化することが可能となりました。

合成されたコードは、Altera® Stratix II FPGAにプロトタイプとして実装されました。最終的に、同じSimulinkモデルから生成されたHDLコードを合成し、ASIC用のIPコアが合成されました。

ルネサスのエンジニアは、SimulinkおよびHDL Coderを使用して、画像処理IPコアの開発をすでに完了しており、将来、同様の画像処理技術プロジェクトでもモデルベース デザインを使用することを計画しています。

結果

- 複数の最適化、選択肢の設計案を調査. 「モデルベース デザインで、私たちは、ビット幅、リソース・シェアリング案、およびパイプライン・レジスタ数を変更し、HDLコードを繰り返し生成することにより、設計を系統的に最適化することができました」と神谷氏は述べています。「これにより、設計の代替案を調査し、要求仕様に適合するようパラメータの最適化を行うことをより容易に実現することができました。」

- 効率的なHDLコードを生成. 「最適化の後に、自動的に生成されたコードは、本質的に私たちの最良の手書きのコードと同様の面積および速度特性を保持していました。」と神谷氏は述べています。「HDL Coderによって生成されたHDLコードは、私たちが手書きで作成した等価なHDLコードと比較して、120MHzおよび275MHzのターゲット・クロック周波数では、手書きよりやや少ないゲート数で実装することができました。」

- 実践的なエンジニア技能を迅速に獲得. 「SimulinkおよびHDL Coderの使用によって、過去にハードウェア経験が無かったエンジニアがRTL設計を約6か月で身に着けることができました」と神谷氏は述べています。「これはたった3名のエンジニアのチームが、同じ期間中にFPGA上で複雑な画像処理アルゴリズムを設計し実装することを可能にするのに役立ちました。」